### 60 A electronic fuse for 12 V DC rail

QFN 32 (5 x 5)

#### **Features**

- · 60 A continuous current

- Input voltage range from 5 to 18 V

- · Adjustable current limit

- Input undervoltage lockout

- Integrated 0.85 mΩ Power MOSFET

- · Enable/Disable pin

- · Programmable turn-on time

- · Accurate current monitor signal

- · Precise temperature monitor

- Overcurrent and Fault status flags

- · Internal MOSFET self-diagnostic

- Parallel operation

- · Thermal protection

- Fault management: latch-off or auto-retry versions

- QFN32- 5 x 5 package

- Temperature range: -40°C to 125°C

### **Applications**

- Server main eFuse

- Hot-swap boards

- High power industrial 12 V rail protection

#### **Maturity status link**

STEF12H60M

### **Description**

The STEF12H60M is a 60 A integrated electronic fuse optimized for monitoring the output current and the input voltage, over the 12 V DC power lines.

When connected in series to the main power rail, it is able to detect and react to overcurrent conditions. When an overload condition occurs, the device limits the output current to a safe value defined by the user.

A precise current monitor signal provides continuous information about the load current to the system controller IC.

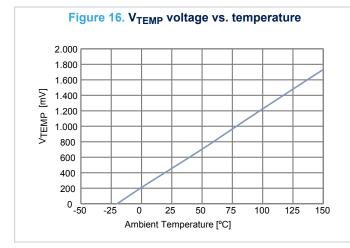

Similarly, a precise temperature sensor generates a monitor signal that permits the system controller to keep the device power dissipation under control.

Turn-on time is programmable, which helps control the inrush current during start-up operations.

Multiple devices can work in parallel and smoothly share the current during the start-up phase, thanks to a dedicated current balancing feature.

The device also embeds the undervoltage lockout feature, self-diagnostic and absolute thermal protection.

# 1 Diagram

Gate  $V_{\mathsf{INF}}$ 5 V LDO  $V_{\text{IN}}$ Copy 2 1 : 10000 Voltage Monitoring circuit SS UT \_\_\_\_ 3.0V R1 OUT R2 10µА  $\rm V_{\rm OUT}$ Overcurrent timer CLREF Current sensor and current monitor Logic  $\mathbf{I}_{\mathsf{MON}}$ cs Safe startup And current limit Reference circuit GND D\_OC comparator D\_OC GND G\_DCH PD ON comparator GOK UVLO G\_OK\_n ON/PD 1.4V Core logic GND 3.7V QFF comparator ON OFF 1.2V Thermal prof Temperature monitoring PD\_OFF V<sub>TEMP</sub> 50µА 0.8V GND GND

Figure 1. Block diagram

DS13608 - Rev 2 page 2/34

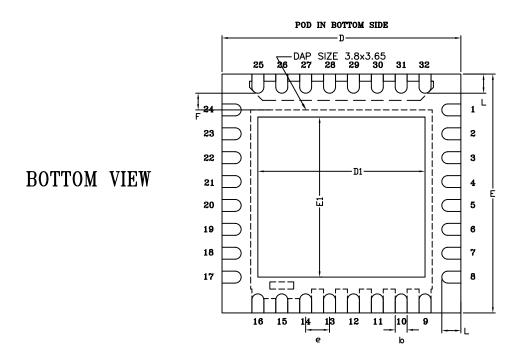

# 2 Pin configuration

$V_{\text{OUT}} \ V_{\text{OUT}} \ V_{\text{OUT}} \ V_{\text{OUT}} \ V_{\text{OUT}} \ V_{\text{OUT}} \ V_{\text{OUT}}$ 32 30 26 25 [28] 27 [8] (24 CLREF NC NC (reserved) **N**) (23 CS D\_OC (22)ω)  $I_{MON}$ ON/PD (21) $V_{DD}$ EXPOSED PAD  $(V_{IN})$ (20) GND GOK တ\_)  $(\boxed{19}]$  SS NC (reserved) <u>ත</u>) **\_\_**)  $(\boxed{18} V_{\text{TEMP}}$  $V_{\mathsf{INF}}$ NC (reserved) **∞**)  $(\overline{17})$  Gate

Figure 2. Pin connection (top view)

Table 1. Pin description

| Pin #   | Symbol            | Function                                                                                                                                                                                                                                                                                                                    |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25 - 32 | V <sub>OUT</sub>  | Output voltage of the eFuse. All pins must be connected together on the PCB                                                                                                                                                                                                                                                 |

| 3       | D_OC              | Output pin, driven low if the current set-point is exceeded. It is a 5 V compliant open drain output                                                                                                                                                                                                                        |

| 4       | ON / PD           | Enable/disable pin. This pin is internally pulled up. Pull this pin below the relevant threshold to shut down the chip. Pull it above threshold to enable the chip. This pin also commands the output pull-down resistance. A capacitor connected between this pin and GND can be used to increase the delay during startup |

| 5       | GOK               | Gate-OK output pin. It signals that a shutdown, which was not commanded by the enable pin, has happened. 5 V compliant open drain output, low when device is in a fault condition                                                                                                                                           |

| 1       | NC                | Not internally connected. It can be connected to any voltage                                                                                                                                                                                                                                                                |

| 6, 8    | NC/reserved       | These pins are reserved and must be left floating                                                                                                                                                                                                                                                                           |

| 2       | NC/reserved       | This pin is reserved. If necessary, it can be connected to any voltage up to V <sub>IN</sub>                                                                                                                                                                                                                                |

| 7       | V <sub>INF</sub>  | Input voltage for internal circuits. It is connected to V <sub>IN</sub> through an R-C filter                                                                                                                                                                                                                               |

| 9 - 16  | V <sub>IN</sub>   | Input voltage of the eFuse. All these pins must be connected together and to the exposed pad                                                                                                                                                                                                                                |

| 17      | Gate              | Gate pin of the internal MOSFET. This pin must be left floating or it can be bypassed to GND through an external R-C filter, to minimize the risk of oscillation in case of very small C <sub>OUT</sub> or high input / output inductance                                                                                   |

| 18      | V <sub>TEMP</sub> | Temperature monitor pin. Bypass to GND with 0.1 µF capacitor                                                                                                                                                                                                                                                                |

DS13608 - Rev 2 page 3/34

| Pin #    | Symbol           | Function                                                                                                                                                                                                                                            |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19       | SS               | Soft-start pin. A capacitor connected between this pin and GND determines the soft-start time. If it is left floating the start-up time is about 300 $\mu s$                                                                                        |

| 20       | GND              | Analog device ground                                                                                                                                                                                                                                |

| 21       | $V_{DD}$         | Internal LDO output and compensation pin. It provides a regulated 5 V auxiliary output. This pin must be bypassed to GND via a 1 $\mu F$ capacitor to ensure the correct functionality of the device                                                |

| 22       | I <sub>MON</sub> | Current monitor pin. A resistor ( $R_{MON}$ ) connected between this pin and GND generates a voltage proportional to the output current. It is suggested to connect a capacitor ( $C_{MON}$ ) in parallel to $R_{MON}$ to filter the monitor signal |

| 23       | CS               | Current feedback. A resistor ( $R_{CS}$ ) connected between this pin and GND provides a feedback voltage for the current limit circuit and the overcurrent indicator ( $D_{CS}$ ). Do not connect any capacitance to this pin                       |

| 24       | CLREF            | Current limit set-point pin. Connect a resistor to GND or force an external control voltage to define the current limit set-point                                                                                                                   |

| EXP. PAD | V <sub>IN</sub>  | Input voltage, internally connected to the power FET drain                                                                                                                                                                                          |

DS13608 - Rev 2 page 4/34

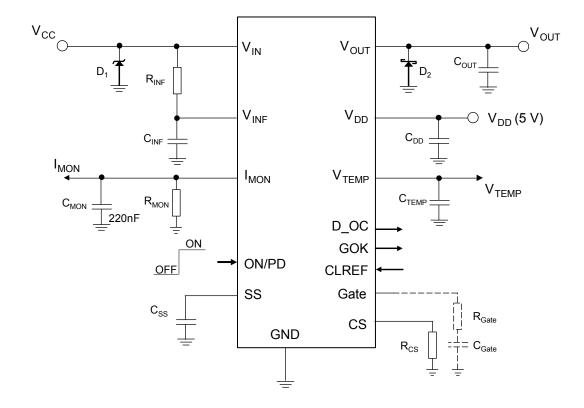

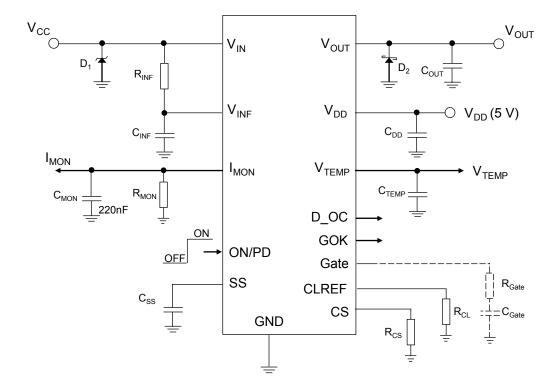

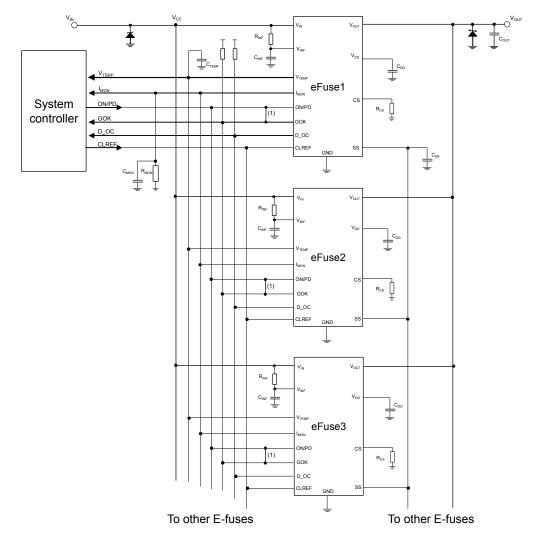

# 3 Typical application

Figure 3. Typical application diagram (external controller used for C<sub>LREF</sub> pin)

DS13608 - Rev 2 page 5/34

Figure 4. Typical application diagram (current limit fixed via R<sub>CL</sub>)

DS13608 - Rev 2 page 6/34

Figure 5. Typical application diagram (multiple e-fuses in parallel)

Note: Connect all the GOK and ON/PD pins when using the auto-retry version (STEF12H60MAPUR) in parallel configuration, to achieve synchronous restart cycle. Refer to Section 6.11 Parallel operation for further details.

DS13608 - Rev 2 page 7/34

## 4 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol             | Parameter                      | Value       | Unit |

|--------------------|--------------------------------|-------------|------|

| V <sub>IN</sub>    | Input supply voltage           | -0.3 to 20  | V    |

| V <sub>INF</sub>   | Input supply voltage           | -0.3 to VIN | V    |

| V <sub>OUT</sub>   | Output voltage                 | -0.3 to VIN | V    |

| V <sub>DD</sub>    | LDO output voltage             | -0.3 to 7   | V    |

| All other pins     | Pin voltage                    | -0.3 to 6   | V    |

| I <sub>OUT</sub>   | Continuous output current      | 75          | Α    |

| I <sub>DD</sub>    | LDO continuous output current  | 60          | mA   |

| ESD                | Charge device model            | ± 500       | V    |

| LSD                | Human body model               | ± 2000      | V    |

| T <sub>J-OP</sub>  | Operating junction temperature | -40 to 125  | °C   |

| T <sub>J-MAX</sub> | Maximum junction temperature   | 150         | °C   |

| T <sub>STG</sub>   | Storage temperature            | -55 to 150  | °C   |

<sup>1.</sup> The thermal limit is set above the maximum operating temperature. It is not recommended to operate the device at temperatures greater than the maximum ratings for extended periods of time.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Exposure to absolute-maximum-rated conditions may affect device reliability.

Table 3. Thermal data

| Symbol | Parameter                           | Value  | Unit |

|--------|-------------------------------------|--------|------|

| P.,    | Thermal resistance junction-ambient | 26 (1) | °C/W |

| KthJA  | mermai resistance junction-ambient  | 22 (2) | C/VV |

<sup>1.</sup> JEDEC still air natural convection test as per JESD 51-2 A, at ambient temperature of 25 °C by using JEDEC (JESD 51-7) 4L PCB FR4 board using 1 sq-in pad, 1 oz Cu.

Note:

Functional operation beyond the recommended operating conditions is not implied.

DS13608 - Rev 2 page 8/34

<sup>2.</sup> Forced moving air environment (100 LFM).

Table 4. Recommended operating conditions

| Symbol             | Parameter                           | Test conditions          | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------------------|--------------------------|------|------|------|------|

| V <sub>IN</sub>    | Input voltage                       |                          | 8    | 12   | 15   | V    |

| I <sub>OUT</sub>   | Continuous output current           |                          |      |      | 60   | Α    |

| I <sub>DD</sub>    | LDO continuous output current       | V <sub>INF</sub> = 5.5 V |      |      | 50   | mA   |

| R <sub>CS</sub>    | Current set resistor                |                          | 1.8  |      | 4    | kΩ   |

| V <sub>CLREF</sub> | Control voltage range               |                          | 0.2  |      | 1.4  | V    |

| C <sub>OUT</sub>   | Output capacitance (1)              |                          | 47   |      |      | μF   |

| t <sub>ss</sub>    | Soft-start duration                 |                          | 10   | 50   | 100  | ms   |

| C <sub>DD</sub>    | V <sub>DD</sub> capacitor value (2) |                          | 1    | 2.2  | 10   | μF   |

The maximum allowed output capacitance to obtain a successful startup, without triggering internal fault protections, depends on the device soft-start time, R<sub>CS</sub> resistor and output load during power-up.

Note: Functional operation beyond the recommended operating conditions is not implied.

DS13608 - Rev 2 page 9/34

<sup>2.</sup>  $V_{DD}$  capacitor is mandatory to ensure the internal regulator stability and the device functionality.

## **5** Electrical characteristics

$T_J$  = -40 °C to +125 °C, typical values refer to  $T_J$  = 25 °C,  $V_{IN}$  =  $V_{INF}$  = 12 V,  $V_{ON/PD}$  = 3.3 V;  $C_{OUT}$  = 100  $\mu$ F; unless otherwise specified. Min. and max. values are guaranteed by design and characterization through statistical correlation.

**Table 5. Electrical characteristics**

| Symbol                  | Parameter                                                                      | Testconditions                                                                           | Min. | Тур.     | Max. | Unit                    |

|-------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|----------|------|-------------------------|

| Input section           | n                                                                              |                                                                                          |      | <u>'</u> |      |                         |

| V <sub>IN</sub>         | Operating input voltage                                                        |                                                                                          | 5    | 12       | 18   | V                       |

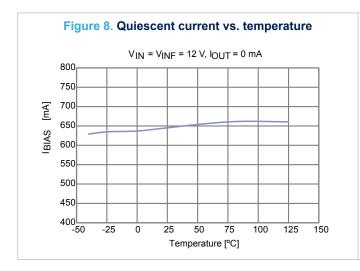

|                         |                                                                                | Device operating, no load (V <sub>ON/PD</sub> > 1.4 V)                                   |      | 650      | 1000 |                         |

| $I_{q}$                 | I <sub>q</sub> Quiescent current                                               | Fault condition                                                                          |      | 300      |      | μA                      |

|                         |                                                                                | Off-state, V <sub>ON/PD</sub> = 0 V, V <sub>INF</sub> = 16 V                             |      | 200      | 400  |                         |

| LDO                     |                                                                                |                                                                                          |      |          |      |                         |

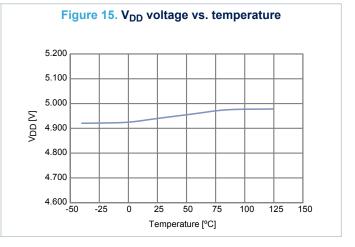

| V <sub>DD</sub>         | LDO output voltage                                                             | I <sub>DD</sub> = 1 mA, V <sub>INF</sub> = 6 V                                           | 4.6  | 4.9      | 5.2  | V                       |

| I <sub>DDmax</sub>      | LDO short-circuit current (1)                                                  | V <sub>DD</sub> = 0 V                                                                    | 60   | 120      | -    | mA                      |

| V <sub>DROP</sub>       | LDO dropout voltage                                                            | I <sub>DD</sub> = 30 mA                                                                  | 66   | 100      | 160  | mV                      |

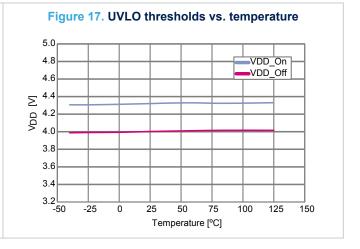

| V <sub>DD ON</sub>      | UVLO rising threshold                                                          | -DD                                                                                      | 4.1  | 4.3      | 4.6  | V                       |

| V <sub>DD</sub> OFF     | UVLO falling threshold                                                         |                                                                                          | 3.8  | 4.0      | 4.2  | V                       |

| Startup                 | OVEO failing threshold                                                         |                                                                                          | 3.0  | 4.0      | 4.2  | V                       |

| I <sub>SS</sub>         | Soft-start capacitor charging current                                          |                                                                                          | 4.5  | 5.2      | 6    | μA                      |

| t <sub>SSMAX</sub>      | Soft-start max. time                                                           | If V <sub>OUT</sub> < 90% of V <sub>IN</sub> after T <sub>SSMAX</sub> shutdown is forced |      | 200      |      | ms                      |

| As                      | Soft-start gain                                                                | Relation between internal soft-start signal ramp and V <sub>OUT</sub>                    |      | 10       |      | V/V                     |

| PowerMOSF               | ET                                                                             |                                                                                          |      |          |      |                         |

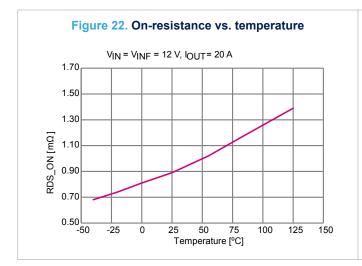

| R <sub>DSon</sub>       | On-resistance                                                                  | T <sub>J</sub> = 25 °C                                                                   |      | 0.85     | 1.1  | mΩ                      |

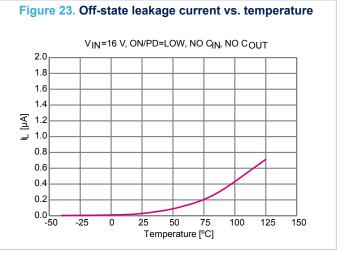

| ΙL                      | Off-state leakage current                                                      | V <sub>ON/PD</sub> = 0 V, V <sub>IN</sub> = 16 V, T <sub>J</sub> = 25 °C                 |      |          | 1    | μA                      |

| Current limit           | t and current monitor circui                                                   | <u> </u>                                                                                 |      |          |      |                         |

| V <sub>CS_TH</sub>      | Current limit activation threshold (V <sub>CS</sub> = IRCS x R <sub>CS</sub> ) | V <sub>OUT</sub> > 80% of V <sub>IN</sub>                                                | 97   | 100      | 103  | % of V <sub>CLREF</sub> |

| V <sub>CL_MAX</sub> (2) | Maximum CL reference voltage                                                   |                                                                                          | 1.5  | 1.6      | 1.65 | V                       |

| V <sub>CL_FD</sub>      | Internal voltage reference for foldback current limit at startup               | V <sub>OUT</sub> is lower than 40% of V <sub>IN</sub> 130                                |      | 150      | 170  | mV                      |

| V <sub>CL_ST</sub>      | Internal voltage reference for current limit at startup                        | V <sub>OUT</sub> is between 40% and 80% 470 500                                          |      | 500      | 530  | mV                      |

| t <sub>CL</sub>         | Current limit response time                                                    | From V <sub>CS</sub> > V <sub>CLREF</sub> until current imit                             |      | 100      |      | μs                      |

| I <sub>CL</sub>         | C <sub>L</sub> pin internal biasing current                                    | From C <sub>L</sub> pin into 1 V source                                                  | 9.4  | 10       | 10.4 | μA                      |

DS13608 - Rev 2 page 10/34

| Symbol                             | Parameter Testconditions                                             |                                                                                                                | Min. | Тур. | Max. | Unit                   |  |

|------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------------------------|--|

| V <sub>CL_HI</sub>                 | Maximum voltage of the C <sub>LREF</sub> pin internal biasing source |                                                                                                                |      | 3.0  |      | V                      |  |

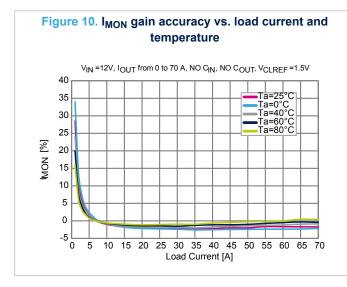

| I <sub>RCS</sub> /I <sub>MON</sub> | Current sense/monitor accuracy                                       | T <sub>J</sub> = 25 °C, 10 A < I <sub>OUT</sub> < 60 A <sup>(3)(4)</sup>                                       | -3   |      | 3    | %                      |  |

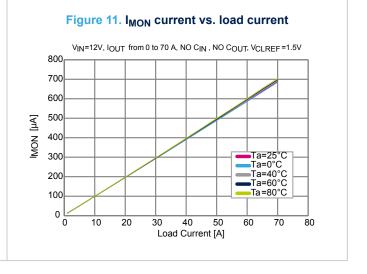

| A <sub>CS</sub> , A <sub>MON</sub> | Current sense and current monitor gain                               | $I_{RCS}/I_{OUT}$ , $I_{MON}/I_{OUT}$ ,<br>$I_{j} = 25  ^{\circ}C$ , 10 A < $I_{OUT}$ < 60 A $^{(3)}$ $^{(4)}$ | 9.7  | 10   | 10.3 | μA/A                   |  |

| t <sub>SH</sub>                    | Shutdown timer (3)                                                   | From current limit detection to MOSFET turn-off                                                                |      | 250  |      | μs                     |  |

| I <sub>SC</sub>                    | Short-circuit current limit (3)                                      |                                                                                                                |      | 100  |      | Α                      |  |

| T <sub>SC</sub>                    | Short-circuit protection responsetime (3)                            | From I <sub>OUT</sub> > I <sub>SC</sub> until MOSFET gate pulldown                                             |      | 500  |      | ns                     |  |

| V <sub>MON_MAX</sub>               | Internal current source maximum voltage                              | Internal pullup voltage on IMONpin                                                                             |      | 3.0  |      | V                      |  |

| ON/PD (chip                        | enable pin)                                                          |                                                                                                                |      |      |      |                        |  |

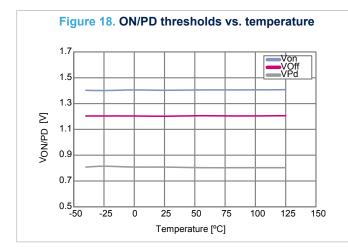

| V <sub>OFF</sub>                   | Low level input voltage                                              | Output disabled/PD activated                                                                                   | 1.11 | 1.2  | 1.29 | V                      |  |

| V <sub>ON</sub>                    | High level input voltage                                             | Output enabled                                                                                                 | 1.3  | 1.4  | 1.5  | V                      |  |

| V <sub>PD</sub>                    | Pull down deactivation threshold                                     | Pulldown deactivated                                                                                           | 0.71 | 0.8  | 0.89 | V                      |  |

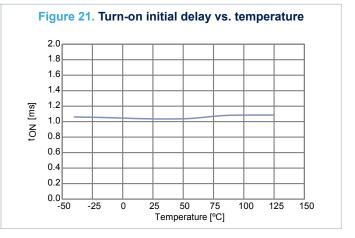

| t <sub>ON</sub>                    | Initial delay time                                                   | From V <sub>ON/PD</sub> >V <sub>ON</sub> to soft-start beginning                                               | 0.8  | 1    | 1.2  | ms                     |  |

| I <sub>ON/PD</sub>                 | Enable pin bias current                                              |                                                                                                                | 4    | 5    | 6    | μA                     |  |

| V <sub>ON/PD_MAX</sub>             | Internal current source maximum voltage                              | Internal pullup voltage on ON/PD pin                                                                           |      | 3.0  |      | V                      |  |

| R <sub>PD</sub>                    | Output pull-down resistance                                          | V <sub>OUT</sub> = 12 V, pulldown activated                                                                    |      | 0.72 |      | kΩ                     |  |

| t <sub>PD</sub>                    | Output pull-down delay timer                                         | From V <sub>OFF</sub> <v<sub>ON/PD <v<sub>PD</v<sub></v<sub>                                                   |      | 2    |      | ms                     |  |

| Temperature                        | monitor                                                              |                                                                                                                |      |      |      |                        |  |

|                                    | V <sub>TEMP</sub> voltage                                            | T = 25 °C                                                                                                      |      | 450  |      | mV                     |  |

| $V_{TEMP}$                         | Temp coefficient (3)                                                 | T = 0 °C to 125 °C                                                                                             |      | 10   |      | mV/°C                  |  |

| V IEMP                             | Load capability                                                      | Maximum current                                                                                                |      |      | 4    | mA                     |  |

|                                    | Pull-down current                                                    | T = 25 °C                                                                                                      |      | 50   |      | μA                     |  |

| Status line                        |                                                                      |                                                                                                                |      |      |      |                        |  |

| COK                                | Gate-OK output voltage                                               | I <sub>SINK</sub> = 1 mA                                                                                       |      |      | 0.1  | V                      |  |

| GOK                                | Leakage current                                                      | V <sub>GOK</sub> = 5 V                                                                                         |      |      | 1    | μA                     |  |

| V <sub>oc</sub>                    | Overcurrent detection threshold                                      | V <sub>CS</sub> voltage threshold that triggers D_OC low                                                       | 83   | 85   | 87   | %<br>V <sub>CLRE</sub> |  |

| D_OC                               | Overcurrent monitor signal active low voltage                        | I <sub>SINK</sub> = 1 mA V <sub>CS</sub> > V <sub>OC</sub>                                                     |      |      | 0.1  | V                      |  |

| 00                                 | Leakage current                                                      | $V_{D\_OC} = 5 V V_{CS} < V_{OC}$                                                                              |      |      | 1    | μA                     |  |

| T <sub>D</sub>                     | D_OC signal response time (3)                                        |                                                                                                                |      | 1    |      | μs                     |  |

| Thermal pro                        | tection                                                              |                                                                                                                |      |      |      | -                      |  |

| T <sub>SD</sub>                    | Shutdown temperature (3)                                             | GOK pulled low                                                                                                 | 130  | 140  | 150  | °C                     |  |

DS13608 - Rev 2 page 11/34

| Symbol               | Parameter                                     | Testconditions                                                                                | Min. | Тур. | Max. | Unit                    |

|----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|-------------------------|

| T <sub>Retry</sub>   | Autoretrydelay time (only on STEF12H60MAPUR)  | From shutdown due to fault to automatic restart.                                              |      | 1    |      | s                       |

| Internal MOS         | SFET diagnostics                              |                                                                                               |      |      |      |                         |

| V <sub>DS_TH</sub>   | Drain-source short detection threshold        | If V <sub>OUT</sub> > V <sub>DS_TH</sub> at startup, startup is postponed                     |      | 90   |      | % of<br>VIN             |

| V <sub>DS_OK</sub>   | Drain-source voltage good detection threshold | If V <sub>OUT</sub> < V <sub>DS_OK</sub> startup is resumed                                   |      | 70   |      | % of<br>VIN             |

| V <sub>OUT_LOW</sub> | Low V <sub>OUT</sub> detection threshold      | After startup, if V <sub>OUT</sub> < V <sub>OUT_LOW</sub> , the device is turned off          |      | 90   |      | % of<br>V <sub>IN</sub> |

| $V_{DG\_SH}$         | Gate-drain short detection voltage threshold  | If V <sub>G</sub> > V <sub>DG_SH</sub> after enable by ON pin, startup is postponed           |      | 3.1  |      | V                       |

| V <sub>DG_OK</sub>   | Gate-drain voltage good detection threshold   | If V <sub>G</sub> < V <sub>DG-OK</sub> startup is resumed                                     |      | 3    |      | V                       |

| $V_{G\_LOW}$         | Gate fault detection threshold                | If V <sub>GD</sub> < V <sub>G_LOW</sub> device is turned off                                  |      | 5.7  |      | V                       |

| $T_{G\_LOW}$         | Gate fault timer in normal operation          | After $T_{SSMAX}$ elapses, time from $V_{GD} < V_{G\_LOW}$ transition to gate fault detection |      | 200  |      | ms                      |

<sup>1.</sup> Pulsed test. The internal LDO is not equipped with thermal protection. Short-circuit duration must not be longer than 1 ms to avoid damage.

- 3. Guaranteed by design, but not tested in production.

- 4. MOSFET fully conducting, at minimum R<sub>ON</sub>.

DS13608 - Rev 2 page 12/34

<sup>2.</sup> If the voltage on CLREF pin is higher than V<sub>CL\_MAX</sub> internal reference, the current limit reference voltage is clamped to V<sub>CL\_MAX</sub>.

### 6 Device functional description

The STEF12H60M is a 12 V electronic fuse (eFuse), which is able to limit the current during fault events, such as output overload or short-circuit.

The current limiting loop is also used during the start-up phase of the eFuse to avoid startups into faulty loads. During normal operation, the eFuse works as a low-resistance power switch, therefore the output voltage follows the input one. In case of overcurrent event, the eFuse limits the  $V_{GS}$  of the internal MOSFET switch, in order to clamp the output current to a safe value.

If the fault persists, after a predefined safety timer, or in case the die temperature hits the thermal protection threshold, due to the increased power dissipation, the device goes into shutdown, the internal switch is turned off and the load is disconnected from the power supply. The device is latched in this off-state until a power supply re-cycle is performed. The auto-retry version instead, is able to re-try starting the device after a fault event, with a typical delay of 1 ms.

The current limit and soft-start features are programmable by the user, through external components.

#### 6.1 UVLO ON/PD function

The device is supplied through the  $V_{IN}$  pins, which carry the power directly to the internal power MOSFET drain connection, and the  $V_{INF}$  pin, which is the input of the internal regulator, used to supply the analog and logic circuits. This pin must be connected externally to  $V_{IN}$  through an R-C filter (see Section 3 Typical application).

The UVLO (undervoltage lockout) monitors the voltage of the internally regulated  $V_{DD}$  node and turns on the device when  $V_{DD} > V_{DD\_ON}$  (typically 4.3 V). If  $V_{DD}$  falls below the UVLO hysteresis threshold ( $V_{DD} < V_{DD\_OFF}$ ), the device is turned off including the reset of fault state.

#### 6.2 ON/PD function

During turn-on, provided that the UVLO rising threshold has been surpassed, the start-up procedure begins once the device is enabled via the ON/PD pin. The ON/PD is a logical input with a dual functionality, according to the following description:

- 1. Enable/disable the device: when V<sub>ON/PD</sub> > V<sub>ON</sub>, the device is enabled. If V<sub>ON/PD</sub> is pulled down to V<sub>OFF</sub> or a lower voltage, the device is disabled and the output is shut down. In case the shutdown occurred due to a fault (thermal, overcurrent, failed startup), the device cannot be turned on again via the ON/PD pin. To reset the device from this latched status, a power supply re-cycle is necessary. Alternatively, a reset can be forced without turning off the power supply, by pulling V<sub>DD</sub> pin below the UVLO voltage and then releasing it.

- Activate/deactivate the output discharge feature (PD output pulldown): if V<sub>ON/PD</sub> is kept between V<sub>PD</sub> (typ. 0.8 V) and V<sub>OFF</sub> (typ. 1.2 V) for at least 2 ms (t<sub>PD</sub>), the integrated 0.77 kΩ R<sub>PD</sub> discharging resistor is connected between V<sub>OUT</sub> and GND

The ON/PD pin has an internal pull-up current generator connected to the internal LDO, therefore, if the pin is not connected to an external controller IC, it goes to the ON-state (device enabled).

The 5  $\mu$ A ON/PD bias current can be used to charge an external capacitor; in this manner prolonging the initial delay time, defined as the time interval between power supply reaching the UVLO threshold and the output voltage controlled ramp-up initialization.

#### 6.3 Soft-start

The device provides monotonic, controlled start-up ramp, in order to keep the inrush current under control. The output voltage rise time can be set by an external  $C_{SS}$ , which is charged with a constant current during the start-up phase. The soft-start range is adjustable from 1 to 100 ms.

Given the required ramp-up time, the CSS capacitance can be calculated according to the following equation:

$$C_{SS} = N \times \frac{(t_{SS} \times I_{SS} \times 10)}{V_{IN}} \tag{1}$$

where V<sub>IN</sub> is typically 12 V, t<sub>SS</sub> is in the 10-100 ms range and N is the number of eFuses in parallel.

DS13608 - Rev 2 page 13/34

90

76.2

The table below shows typical values of soft-start duration calculated with standard capacitors and typical I<sub>SS</sub> value.

Symbol

Value

C<sub>SS</sub> (nF)

47

82

120

180

220

270

330

390

41.5

50.8

62.3

Table 6. Output voltage rise time vs. C<sub>SS</sub> value (V<sub>IN</sub> = 12 V)

**Important:** Soft-start capacitor must be always connected to ensure controlled operation during startup. In case of absence/bad connection of the  $C_{SS}$ , the start-up phase is short (300  $\mu$ s). This might result in significantly high charging current, eventually leading to the device shutdown for an overcurrent/overtemperature fault. To prevent the device from starting in faulty loads (such as: resistive load, or damaged bulk output capacitors) the following start-up control flow is applied:

- Start-up fold-back current limit: current limit value during start-up phase is dependent on the sensed output

voltage. At the very beginning of startup, when the output voltage is close to zero, the current limit internal

reference voltage is reduced to V<sub>CL\_FD</sub>. Any higher current limit value set by the user via the C<sub>LREF</sub> pin is

overridden by the device

- Start-up current limit: during the ramp-up phase, the current limit internal reference voltage is reduced to V<sub>CL ST</sub>. Any higher current limit value, set by the user via the C<sub>LREF</sub> pin, is overridden by the device

- Maximum start-up time: startup longer than 200 ms is always aborted by the device. If V<sub>OUT</sub> does not reach 90% of V<sub>IN</sub> in 200 ms, the device is turned off and the GOK fault indicator is asserted low

Normal  $C_{LREF}$  functionality is resumed at the end of the start-up phase ( $V_{OUT} > 80 \%$  of  $V_{IN}$ ). Adding a capacitor in parallel to the ON/PD pin, the initial  $t_{ON}$  delay time between valid  $V_{IN}$  value and controlled output ramp-up start ( $V_{OUT} = 1 \text{ V}$ ) can be increased.

The default delay time without C<sub>ON</sub> capacitor is typically 1.25 ms.

18.9

10.8

27.7

#### 6.4 Normal operating conditions

T<sub>SS</sub> (ms)

Once the start-up phase ends, the STEF12H60M eFuse behaves like a mechanical fuse, supplying the load connected to its output with the same voltage shown at its input, minus the small voltage fall due to the N-channel MOSFET  $R_{DS(on)}$ . The status line open-drain indicators GOK and D\_OC provide information about the status of the device.

### 6.5 Current sensing and current limit

When an overload event occurs, the current limiting circuit reduces the conductivity of the power MOSFET, in order to clamp the output current at the value defined by the user by the voltage set on  $C_{LREF}$  pin. Current limit function consists of two sub-circuits:

the current sense (CS) circuit, responsible for sensing the load current and providing a feedback signal to

detect overcurrent. It relies on a small copy-MOSFET built into the integrated power MOSFET to generate a

replica of the load current; proportional by A<sub>CS</sub> = I<sub>RCS</sub>/I<sub>OUT</sub> = 10 μA/A, into the external R<sub>CS</sub> resistor attached

to the eFuse.

DS13608 - Rev 2 page 14/34

This current creates a variable V<sub>CS</sub> voltage across the resistor, defining the eFuse working current CS, which is continuously compared to the current limit reference voltage present on the CLREF pin.

• the current limit (CL) circuit defines the reference threshold for the intervention of the current limitation function. This reference point is a voltage (V<sub>CLREF</sub>) usually provided externally by the system control IC to the CLREF pin, and continuously compared internally to the feedback signal from CS circuit. In this manner, the current limit point can be throttled to satisfy the system power requirements during operation. In simple standalone designs, such as the one shown in Figure 4. Typical application diagram (current limit fixed via R<sub>CL</sub>), where no control IC is present, the reference signal can be generated by connecting a resistor between CLREF pin and GND. An integrated bias generator sources 10 μA of current to the R<sub>CL</sub> resistor, generating a fixed V<sub>CLREF</sub>, which sets the current limit thresholds. To ensure reliability, the signal on CLREF is internally clamped to V<sub>CL\_MAX</sub>, therefore, even in case of wrong signal provided externally on the pin, a safety current limit threshold is always present.

An overcurrent event is detected when the voltage on the CS pin overcomes the  $V_{OC}$  threshold, which is typically 85% of the voltage at the CLREF pin ( $V_{CS} > V_{OC}$ ). In this case the status D\_OC indicator is pulled down. If the load status reverts to normality ( $V_{CS}$  falls below 75% of  $V_{CLREF}$ ), D\_OC is released. Based on the value of the R<sub>CS</sub> resistor, the load current level for D\_OC triggering can be evaluated by using the following equation:

$$I_{OUT} = \frac{V_{OC}}{R_{CS} \times A_{CS}} \tag{2}$$

In case of overcurrent detection, when  $V_{CS}$  surpasses  $V_{CLREF}$ , the  $V_{GS}$  of the internal MOSFET is immediately modulated in order to clamp the load current to the  $I_{LIM}$  value defined by the user via the CLREF pin, according to the following:

$$I_{LIM} = \frac{V_{CLREF}}{R_{CS} \times A_{CS}} \tag{3}$$

During current limitation, additional protection features are activated, in order to keep the total power dissipation under control and protect the device and the system. In particular, a 250  $\mu$ s current limit timer ( $t_{SH}$ ) starts after overload detection. Once the timer elapses, the internal MOSFET is shut down and the GOK indicator is pulled to low status, to inform the system controller that a shutdown not due to ON/PD (fault) occured.

Moreover, due to high power dissipation in current limit condition, if the die temperature increases too much and hits the thermal protection threshold (140 °C typ.), the thermal protection intervenes, turning off the internal MOSFET and asserting GOK low.

A second level current limit (I<sub>SC</sub>) is quickly activated in case the load current surpasses 100 A.

This additional protection, fixed by design, is able to respond to short-circuit events on the output. In such an occurrence, the device is immediately shut down and the D\_OC pin is asserted.

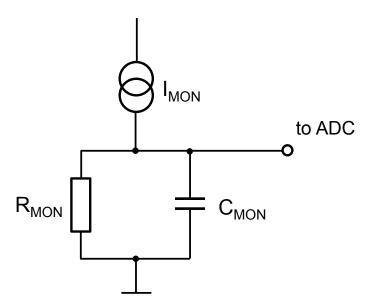

#### 6.6 Current monitor

The device is equipped with a current monitoring capability that allows the system controller to read the current flowing through the fuse. An  $I_{MON}$  current proportional to the load current flowing through the eFuse is imposed on an external  $R_{MON}$ , converting the sensed current into a voltage for further processing by the ADC. The  $I_{MON}$  signal is the output of a chopper amplifier, therefore an external bypass capacitor is suggested to reduce the output ripple and to provide a smooth signal (see figure below). The suggested minimum value for the filter capacitor is 3.9 nF. Lower values result in a worse ripple amplitude.

DS13608 - Rev 2 page 15/34

The current, monitoring amplifier gain and defined as  $A_I = I_{MON} / I_{OUT}$ , is typically 10  $\mu$ A/A.

Figure 6. Current monitor simplified circuit

### 6.7 Temperature monitor and thermal shutdown functions

The STEF12H60M embeds two thermal sensors, each one accomplishing a specific function:

- Overtemperature sensor: this is embedded into the power MOSFET. It monitors the power MOSFET temperature, which is subjected to very fast increases during overload events. If the device temperature exceeds the thermal threshold, typically 140 °C, the thermal shutdown circuit turns the power MOSFET off, thus disconnecting the load. The GOK pin is pulled down. The thermal shutdown protection is always active and overrides any other protection/control feature of the device.

- Temperature sensor: this consists of precise thermal sensors embedded in the controller die. The purpose

is to statically monitor the overall device temperature, and generate a precise monitor signal (V<sub>TEMP</sub>)

accordingly. Overall typical accuracy is +/- 5 °C. To ensure a stable regulation of the temperature monitor

signal in all operating conditions, it is recommended to bypass this pin to GND via a 0.1 μF C<sub>TEMP</sub> capacitor,

as shown in Figure 3 and Figure 4.

The device can be reset from a thermal shutdown condition by pulling the  $V_{DD}$  pin below the UVLO threshold or by re-cycling the supply voltage.

In parallel configuration, to accomplish simultaneous reset, each device must have its dedicated reset switch, for instance a MOSFET. All the gates of the reset MOSFETS must be tied together to the common reset signal.

### 6.8 Status indicators and fault conditions

Two open-drain flags can be used to monitor the status of the eFuse, along with the current and temperature monitor signals.

- D\_OC Overcurrent indicator: in normal operation and during startup it is released. It is pulled down upon detection of an overload (see Section 6.5 Current sensing and current limit)

- GOK gate ok indicator: this indicator informs that there was a shutdown that was not commanded by the enable pin (ON/PD). In particular, this pin is pulled low when:

- too low input voltage: V<sub>DD</sub> lower than UVLO threshold

- too long start-up time: V<sub>OUT</sub> does not reach 90% of V<sub>IN</sub> in 200 ms

- too long current limit: a current limit event is longer than t<sub>SH</sub> (250 μs typ.)

DS13608 - Rev 2 page 16/34

During the startup, GOK is released once UVLO is reached, under the condition that  $V_{out}$  is below  $V_{DS\_OK}$  (drain to source short detection, see Section 6.9 ), therefore it cannot be used directly as a Power Good flag. GOK is also pulled to low level in the case of any of the faults described in Section 6.9 .

### 6.9 Diagnostic functions and protections

The STEF12H60M embeds several internal diagnostic features that prevent fault condition induced internally that may affect the application (refer to Section 5 Electrical characteristics):

- Power MOSFET gate leakage check during startup and normal operation (V<sub>Gate</sub>-V<sub>IN</sub> < 5.6 V)</li>

- Gate shorted-to-V<sub>IN</sub>

- Drain to source short in disabled mode (ON pin low). This protection prevents a new startup until the V<sub>OUT</sub> falls below the V<sub>DS Ok</sub> value.

- V<sub>OUT</sub> too low (V<sub>OUT</sub> < 90% of V<sub>IN</sub>) after soft-start

- V<sub>OUT</sub> does not reach 90% of V<sub>IN</sub> in 200 ms during startup

- Charge pump error

- Pull-down circuit error

In any case of fault, the GOK indicator is pulled down and the soft-start capacitor is discharged.

### 6.10 Latch (STEF12H60MPUR) and auto-retry versions (STEF12H60MAPUR)

The STEF12H60M electronic fuse is offered in two variants that differ in how the device reacts after a fault condition (see Section 6.8 and Section 6.9 ). In particular, the STEF12H60MPUR latches off after a fault and can be reset by pulling the  $V_{DD}$  pin below the UVLO threshold or by re-cycling the supply voltage. The STEF12H60MAPUR instead stays in OFF mode for 1 s. ( $T_{Retry}$ ) and after restarts automatically, initiating a soft-start cycle. The number of restart cycles is not internally limited .

DS13608 - Rev 2 page 17/34

### 6.11 Parallel operation

Figure 5 shows a typical circuit configuration used to protect high power systems. In this case multiple STEF12H60M are used in a parallel configuration to increase the total current capability. In such design the following guidelines must be followed:

- The ON\_PD pins of all eFuses must be tied together to achieve a simultaneous startup.

- All the SS pins must be connected together to a single C<sub>SS</sub> capacitor. The value of this capacitor should

be calculated by using Eq. (1), taking into account that each device provides its I<sub>SS</sub> charging current to the

capacitor. The SS pin is also used to discharge the C<sub>SS</sub> capacitor during shutdown. In case one eFuse

shuts down, the common C<sub>SS</sub> capacitor is discharged causing simultaneous shutdown of all the paralleled

devices.

- All the CLREF pins must be tied together to a single R<sub>CL</sub> resistor or to common V<sub>CLREF</sub> control signal from the system controller to set the current limit reference. When using the R<sub>CL</sub> resistor, the I<sub>CL</sub> bias current coming from each device must be accounted.

- Each CS pin must be connected to a local RS, to ensure the current sensing circuit is able to read the single eFuse current.

- The I<sub>MON</sub> pins can be all tied together to a single R<sub>MON</sub> / C<sub>MON</sub> filter. In this way the I<sub>MON</sub> currents coming

from each eFuse all contribute to the voltage generated on the resistor, that results proportional to the total

system current. If it is necessary to read the single eFuse current, the local R<sub>MON</sub> resistor approach can be

used.

- The V<sub>TEMP</sub> pins can be all tied together in Or-ing configuration, therefore the system controller reads the highest temperature among all the eFuses.

- When needed, all of the D\_OC and all of the GOK fault flag pins can be tied together and pulled up via a single resistor.

- To accomplish simultaneous reset, each device must have its dedicated reset switch, for instance a

MOSFET, connected to V<sub>DD</sub> pin. All the gates of the reset MOSFETS must be tied together to the common

reset signal.

- If the auto-retry version (STEF12H60MAPUR) is used in parallel configuration, dedicated circuital provision should be made. Specifically, it is recommended to connect all the ON/PD pins to the GOK ones as shown in Figure 7 to ensure a proper synchronization of the auto-retry cycle. A common Enable signal can be used to start up the devices.

- During power-up in parallel operation, keeping the load current through each eFuse lower than 1.5 A (typical) helps to prevent overstress in the internal power MOSFETS at each soft-start cycle.

DS13608 - Rev 2 page 18/34

ON/PD

GOK eFuse1

ON/PD

GOK eFuse2

GND

ON/PD

GOK eFuse3

GND

To other E-fuses

Figure 7. Additional connections for multiple STEF12H60MAPUR (autoretry version)

DS13608 - Rev 2 page 19/34

# 7 Typical characteristics

$C_{IN}$  = 1  $\mu$ F;  $C_{OUT}$  = 10  $\mu$ F,  $T_J$  = 25  $^{\circ}$ C unless otherwise specified.

Figure 9. Shutdown current vs. temperature  $V_{IN} = V_{INF} = 12 \text{ V or } 16\text{V}$ ,  $I_{OUT} = 0 \text{ mA}$ 400 Device Off (VINF=16V) Device Off (VINF=12V) 350 Thermal fault 300 I<sub>BIAS</sub> [mA] 250 200 150 100 -50 -25 50 75 100 125 150 Temperature [°C]

DS13608 - Rev 2 page 20/34

0.0 \_\_\_\_

-25

0

V<sub>IN</sub> =12V, I OUT from 0 to 70 A, NO C<sub>IN</sub>, NO C<sub>OUT</sub>, V<sub>CLREF</sub>=1.5V

800.0

700.0

600.0

9

300.0

200.0

100.0

50

Temperature [°C]

75

100

125

150

Figure 13. V<sub>CLREF</sub> threshold vs. temperature

101.0

100.8

100.6

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

100.0

1

Figure 14. CLREF pin bias current vs. temperature 12.0 11.5 11.0 10.5 [FA] 10.0 걸 9.5 9.0 8.5 8.0 \_\_\_ -25 0 25 50 75 100 125 150 Temperature [°C]

DS13608 - Rev 2 page 21/34

Figure 19. ON/PD pin current vs. temperature 7.0 6.5 6.0 ON/PD [µA] 5.5 5.0 4.5 4.0 3.5 -25 0 50 75 100 125 150 Temperature [°C]

7.0

6.5

6.0

4.5

4.0

3.5

3.0

-50 -25 0 25 50 75 100 125 150

Temperature [°C]

DS13608 - Rev 2 page 22/34

DS13608 - Rev 2 page 23/34

DS13608 - Rev 2 page 24/34

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

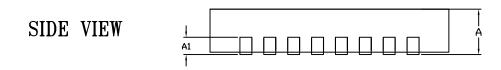

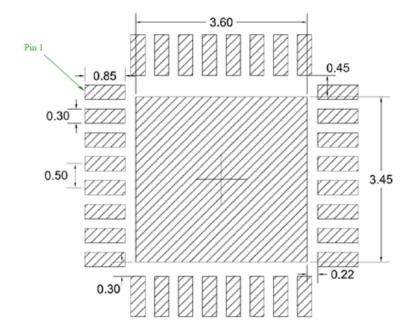

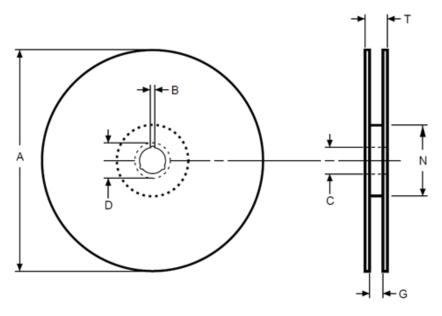

## 8.1 QFN 32 (5 x 5) package information

Figure 34. QFN 32 (5 x 5) package outline

DS13608 - Rev 2 page 25/34

Table 7. QFN 32 (5 x 5) package mechanical data

| Dim.   | mm   |      |      |  |  |  |

|--------|------|------|------|--|--|--|

| Dilli. | Min. | Тур. | Max. |  |  |  |

| А      | 0.90 | 0.95 | 1    |  |  |  |

| A1     |      | 0.20 |      |  |  |  |

| D      | 4.90 | 5.00 | 5.10 |  |  |  |

| D1     | 3.40 | 3.50 | 3.60 |  |  |  |

| E      | 4.90 | 5.00 | 5.10 |  |  |  |

| E1     | 3.25 | 3.35 | 3.45 |  |  |  |

| е      |      | 0.50 |      |  |  |  |

| F      |      | 0.35 |      |  |  |  |

| b      | 0.20 | 0.25 | 0.30 |  |  |  |

| L      | 0.30 | 0.40 | 0.50 |  |  |  |

Figure 35. QFN 32 (5 x 5) recommended footprint

DS13608 - Rev 2 page 26/34

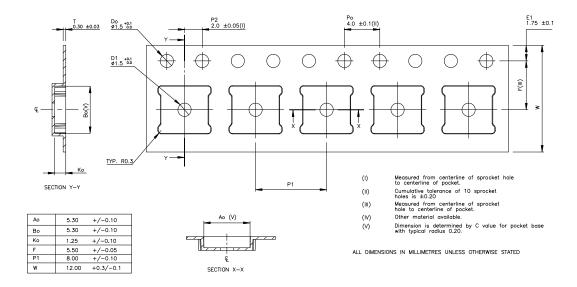

## 8.2 QFN 32 (5 x 5) packing information

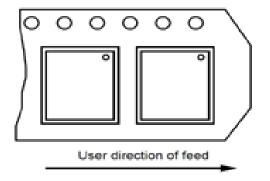

Figure 36. QFN 32 (5 x 5) carrier tape

Figure 37. Pin 1 orientation in tape

DS13608 - Rev 2 page 27/34

Figure 38. QFN 32 (5 x 5) reel outline

Table 8. QFN 32 (5 x 5) reel data

| Reel size | Tape width | A (max.) | B (min.) | С        | D (min.) | G (max.) | N (min.) | T (max.) | Unit |

|-----------|------------|----------|----------|----------|----------|----------|----------|----------|------|

| 13"       | 0.90       | 330      | 1.5      | 13 ± 0.2 | 20.2     | 12.6     | 100      | 18.4     | mm   |

DS13608 - Rev 2 page 28/34

# 9 Ordering information

Table 9. Order codes

| Order code     | Package       | Packaging  | Marking  |

|----------------|---------------|------------|----------|

| STEF12H60MPUR  | OEN22 (5 v 5) | Latch      | EF12M60  |

| STEF12H60MAPUR | QFN32 (5 x 5) | Auto-retry | EF12M60A |

DS13608 - Rev 2 page 29/34

# **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                      |

|-------------|----------|------------------------------|

| 13-Jan-2021 | 1        | Initial release.             |

| 19-Mar-2021 | 2        | Removed footnote in Table 9. |

DS13608 - Rev 2 page 30/34

## **Contents**

| 1   | Diag  | ram                                                            | 2  |

|-----|-------|----------------------------------------------------------------|----|

| 2   | Pin o | configuration                                                  | 3  |

| 3   | Typic | cal application                                                | 5  |

| 4   | Maxi  | imum ratings                                                   | 8  |

| 5   | Elec  | trical characteristics                                         | 10 |

| 6   | Devi  | ce functional description                                      |    |

|     | 6.1   | UVLO ON/PD function                                            | 13 |

|     | 6.2   | ON/PD function                                                 | 13 |

|     | 6.3   | Soft-start                                                     | 13 |

|     | 6.4   | Normal operating conditions                                    | 14 |

|     | 6.5   | Current sensing and current limit                              | 14 |

|     | 6.6   | Current monitor                                                | 15 |

|     | 6.7   | Temperature monitor and thermal shutdown functions             | 16 |

|     | 6.8   | Status indicators and fault conditions                         | 16 |

|     | 6.9   | Diagnostic functions and protections                           | 17 |

|     | 6.10  | Latch (STEF12H60MPUR) and auto-retry versions (STEF12H60MAPUR) | 17 |

|     | 6.11  | Parallel operation                                             | 18 |

| 7   | Typi  | cal characteristics                                            | 20 |

| 8   | Pack  | rage information                                               | 25 |

|     | 8.1   | QFN 32 (5 x 5) package information                             | 25 |

|     | 8.2   | QFN 32 (5 x 5) packing information                             | 27 |

| 9   | Orde  | ering information                                              | 29 |

| Rev | ision | history                                                        | 30 |

## **List of tables**

| Table 1.  | Pin description                                                             | 3 |

|-----------|-----------------------------------------------------------------------------|---|

| Table 2.  | Absolute maximum ratings                                                    | ξ |

| Table 3.  | Thermal data                                                                | ξ |

| Table 4.  | Recommended operating conditions                                            | ć |

| Table 5.  | Electrical characteristics                                                  | ( |

| Table 6.  | Output voltage rise time vs. C <sub>SS</sub> value (V <sub>IN</sub> = 12 V) | 4 |

| Table 7.  | QFN 32 (5 x 5) package mechanical data                                      | 6 |

|           | QFN 32 (5 x 5) reel data                                                    |   |

| Table 9.  | Order codes                                                                 | ć |

| Table 10. | Document revision history                                                   | ( |

DS13608 - Rev 2

# **List of figures**

| Figure 1.  | Block diagram                                                                    | . 2 |

|------------|----------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection (top view)                                                        |     |

| Figure 3.  | Typical application diagram (external controller used for C <sub>LREF</sub> pin) | . 5 |

| Figure 4.  | Typical application diagram (current limit fixed via R <sub>CL</sub> )           | . 6 |

| Figure 5.  | Typical application diagram (multiple e-fuses in parallel)                       | . 7 |

| Figure 6.  | Current monitor simplified circuit                                               | 16  |

| Figure 7.  | Additional connections for multiple STEF12H60MAPUR (autoretry version)           | 19  |

| Figure 8.  | Quiescent current vs. temperature                                                | 20  |

| Figure 9.  | Shutdown current vs. temperature                                                 | 20  |

| Figure 10. | I <sub>MON</sub> gain accuracy vs. load current and temperature                  | 20  |

| Figure 11. | I <sub>MON</sub> current vs. load current                                        | 20  |

| Figure 12. | CS current vs. temperature                                                       | 21  |

| Figure 13. | V <sub>CLREF</sub> threshold vs. temperature                                     | 21  |

| Figure 14. | CLREF pin bias current vs. temperature                                           |     |

| Figure 15. | V <sub>DD</sub> voltage vs. temperature                                          | 21  |

| Figure 16. | V <sub>TEMP</sub> voltage vs. temperature                                        | 21  |

| Figure 17. | UVLO thresholds vs. temperature                                                  | 21  |

| Figure 18. | ON/PD thresholds vs. temperature                                                 | 22  |

| Figure 19. | ON/PD pin current vs. temperature                                                | 22  |

| Figure 20. | SS pin bias current vs. temperature                                              | 22  |

| Figure 21. | Turn-on initial delay vs. temperature                                            | 22  |

| Figure 22. | On-resistance vs. temperature                                                    | 22  |

| Figure 23. | Off-state leakage current vs. temperature                                        | 22  |

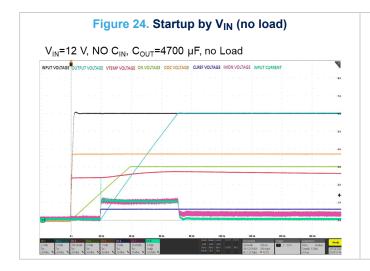

| Figure 24. | Startup by V <sub>IN</sub> (no load)                                             | 23  |

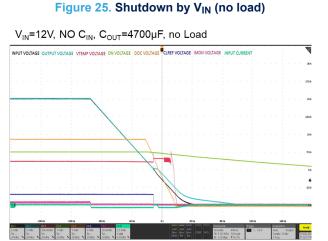

| Figure 25. | Shutdown by V <sub>IN</sub> (no load)                                            | 23  |

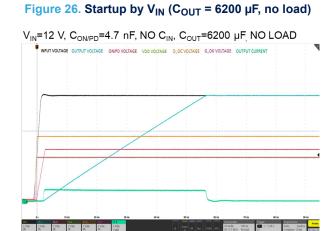

| Figure 26. | Startup by V <sub>IN</sub> (C <sub>OUT</sub> = 6200 μF, no load)                 | 23  |

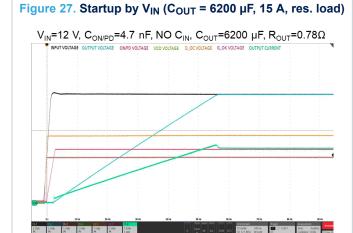

| Figure 27. | Startup by V <sub>IN</sub> (C <sub>OUT</sub> = 6200 μF, 15 A, res. load)         | 23  |

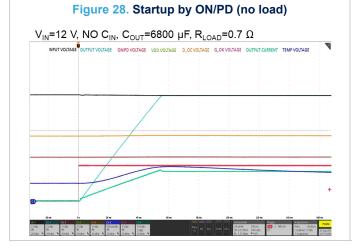

| Figure 28. | Startup by ON/PD (no load)                                                       |     |

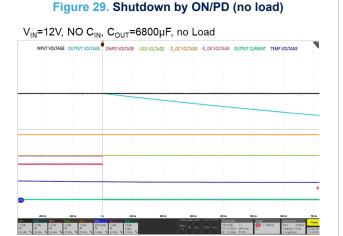

| Figure 29. | Shutdown by ON/PD (no load)                                                      |     |

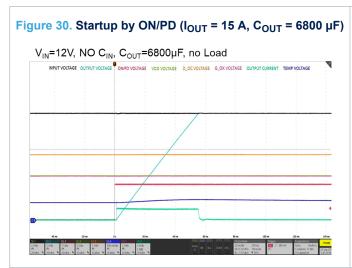

| Figure 30. | Startup by ON/PD (I <sub>OUT</sub> = 15 A, C <sub>OUT</sub> = 6800 μF)           |     |

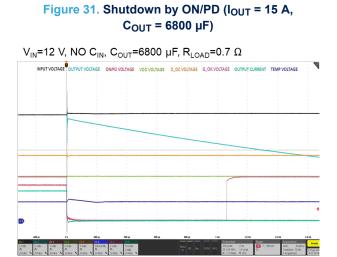

| Figure 31. | Shutdown by ON/PD (I <sub>OUT</sub> = 15 A, C <sub>OUT</sub> = 6800 μF)          | 24  |

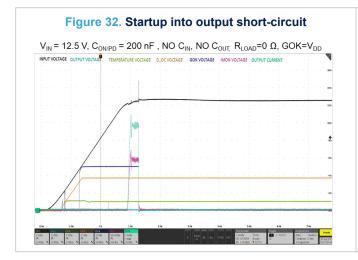

| Figure 32. | Startup into output short-circuit                                                | 24  |

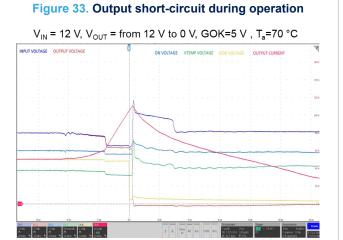

| Figure 33. | Output short-circuit during operation                                            | 24  |

| Figure 34. | QFN 32 (5 x 5) package outline                                                   | 25  |

| Figure 35. | QFN 32 (5 x 5) recommended footprint                                             | 26  |

| Figure 36. | QFN 32 (5 x 5) carrier tape                                                      | 27  |

| Figure 37. | Pin 1 orientation in tape                                                        | 27  |

| Elaura 20  | OFN 22 (F v F) real outline                                                      | 20  |

DS13608 - Rev 2 page 33/34

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13608 - Rev 2 page 34/34

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: STEF12H60MAPUR