# Galvanically isolated 4 A single gate driver

Datasheet - production data

#### **Features**

- 1700 V single channel gate driver

- Driver current capability: 4 A sink / source at 25 °C

- dV/dt transient immunity ± 100 V/ns

- Overall input-output propagation delay: 80 ns

- Separate sink and source for easy gate driving configuration

- 4 A Miller clamp dedicated pin

- UVLO function

- Gate driving voltage up to 26 V

- 3.3 V, 5 V TTL/CMOS inputs with hysteresis

- Temperature shutdown protection

- Standby function

#### **Applications**

- Motor driver for home appliances, factory automation, industrial drives and fans.

- 600/1200 V inverters

- · Battery chargers

- Induction heating

- Welding

- UPS

- Power supply units

- DC-DC converters

- Power factor correction

#### **Description**

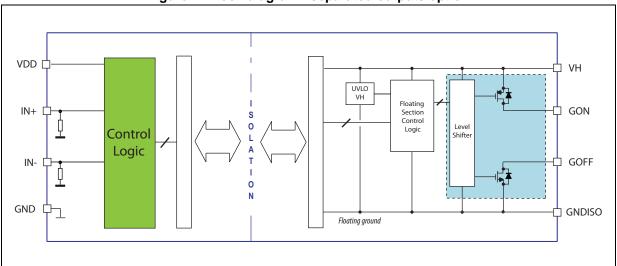

The STGAP2S is a single gate driver which isolates the gate driving channel from the low voltage control and interface circuitry.

The gate driver is characterized by 4 A capability and rail-to-rail outputs, making the device also suitable for high power inverter applications such as motor drivers in industrial applications.

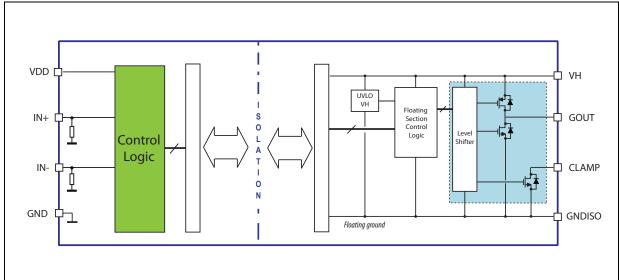

The device is available in two different configurations. The configuration with separated output pins allows to independently optimize turn-on and turn-off by using dedicated gate resistors. A configuration featuring single output pin and Miller clamp function prevents gate spikes during fast commutations in half-bridge topologies.

Both configurations provide high flexibility and bill of material reduction for external components.

The device integrates protection functions: UVLO and thermal shutdown are included to easily design high reliability systems. Dual input pins allow choosing the control signal polarity and also implementing HW interlocking protection in order to avoid cross-conduction in case of controller malfunction.

The input to output propagation delay results contained within 80 ns, providing high PWM control accuracy.

A standby mode is available in order to reduce idle power consumption.

# **Contents**

| Pin description and connection diagram     |                          |  |  |  |

|--------------------------------------------|--------------------------|--|--|--|

|                                            |                          |  |  |  |

| 3.1 Absolute maximum ratings               |                          |  |  |  |

|                                            | 6                        |  |  |  |

| 3.2 Thermal data                           |                          |  |  |  |

| 3.3 Recommended operating conditions       |                          |  |  |  |

| 4 Electrical characteristics               | 7                        |  |  |  |

| 5 Functional description                   | 9                        |  |  |  |

| 5.1 Gate driving power supply and UVLO     | 9                        |  |  |  |

| 5.2 Power up, power down and 'safe state'  | 9                        |  |  |  |

| 5.3 Control inputs                         | 10                       |  |  |  |

| 5.4 Miller clamp function                  | 10                       |  |  |  |

| 5.5 Watchdog                               | 10                       |  |  |  |

| 5.6 Thermal shutdown protection            | 10                       |  |  |  |

| 5.7 Standby function                       | 11                       |  |  |  |

| 6 Typical application diagram              | 12                       |  |  |  |

| 7 Layout                                   | 14                       |  |  |  |

| 7.1 Layout guidelines and considerations   | 14                       |  |  |  |

| 7.2 Layout example                         |                          |  |  |  |

| 8 Testing and characterization information | 16                       |  |  |  |

| 9 Package information                      | 17                       |  |  |  |

| 9.1 SO-8 package information               |                          |  |  |  |

| 10 Suggested land pattern                  | Suggested land pattern19 |  |  |  |

| 11 Ordering information                    | 20                       |  |  |  |

| STGAP2S |                  | Contents |

|---------|------------------|----------|

| 12      | Revision history | <br>21   |

Block diagram STGAP2S

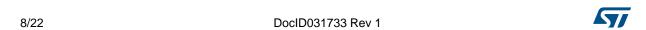

# 1 Block diagram

Figure 1. Block diagram - separated outputs option

Figure 2. Block diagram - single output and Miller clamp option

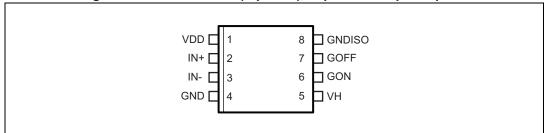

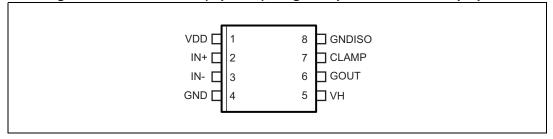

# 2 Pin description and connection diagram

Figure 3. Pin connection (top view), separated outputs option

Figure 4. Pin connection (top view), single output and Miller clamp option

Table 1. Pin description

| Pin      | no.      | Pin name     | Type                                      | Function                              |

|----------|----------|--------------|-------------------------------------------|---------------------------------------|

| Figure 3 | Figure 4 | Pili liaille | Туре                                      | Function                              |

| 1        | 1        | VDD          | Power supply Driver logic supply voltage. |                                       |

| 2        | 2        | IN+          | Logic input                               | Driver logic input, active high.      |

| 3        | 3        | ĪN-          | Logic input                               | Driver logic input, active low.       |

| 4        | 4        | GND          | Power supply                              | Driver logic ground.                  |

| 5        | 5        | VH           | Power supply                              | Gate driving positive voltage supply. |

| -        | 6        | GOUT         | Analog output                             | Sink/source output.                   |

| -        | 7        | CLAMP        | Analog output                             | Active Miller clamp.                  |

| 6        | -        | GON          | Analog output                             | Source output.                        |

| 7        | -        | GOFF         | Analog output                             | Sink output.                          |

| 8        | 8        | GNDISO       | Power supply                              | Gate driving Isolated ground.         |

Electrical data STGAP2S

### 3 Electrical data

## 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol             | Parameter                                                    | Test condition         | Min.  | Max.     | Unit |

|--------------------|--------------------------------------------------------------|------------------------|-------|----------|------|

| VDD                | Logic supply voltage vs. GND                                 | -                      | -0.3  | 6.5      | V    |

| V <sub>LOGIC</sub> | Logic pins voltage vs. GND                                   | -                      | -0.3  | 6.5      | V    |

| VH                 | Positive supply voltage (VH vs. GNDISO)                      | -                      | -0.3  | 28       | ٧    |

| V <sub>OUT</sub>   | Voltage on gate driver outputs (GON, GOFF, CLAMP vs. GNDISO) | -                      | - 0.3 | VH + 0.3 | V    |

| V <sub>iso</sub>   | Input to output isolation voltage (GND vs. GNDISO)           | DC or peak             | -1700 | +1700    | ٧    |

| TJ                 | Junction temperature                                         | -                      | -40   | 150      | °C   |

| T <sub>S</sub>     | Storage temperature                                          | -                      | -50   | 150      | °C   |

| P <sub>Din</sub>   | Power dissipation input chip                                 | T <sub>A</sub> = 25 °C | -     | 10       | mW   |

| P <sub>Dout</sub>  | Power dissipation output chip                                | T <sub>A</sub> = 25 °C | -     | 850      | mW   |

| ESD                | HBM (human body model)                                       | -                      | :     | 2        | kV   |

#### 3.2 Thermal data

Table 3. Thermal data

| Symbol              | Parameter                              | Package | Value | Unit |

|---------------------|----------------------------------------|---------|-------|------|

| R <sub>th(JA)</sub> | Thermal resistance junction to ambient | SO-8    | 130   | °C/W |

# 3.3 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol             | Parameter                                  | Test conditions | Min. | Max. | Unit |

|--------------------|--------------------------------------------|-----------------|------|------|------|

| VDD                | Logic supply voltage vs. GND               | -               | 3    | 5.5  | V    |

| V <sub>LOGIC</sub> | Logic pins voltage vs. GND                 | -               | 0    | 5.5  | V    |

| VH                 | Positive supply voltage (VH vs. GNDISO)    | -               | -    | 26   | V    |

| f <sub>SW</sub>    | Maximum switching frequency <sup>(1)</sup> | -               | -    | 4    | MHz  |

| T <sub>IN</sub>    | Pulse width at IN+, IN-                    | -               | 100  | -    | ns   |

| $T_J$              | Operating junction temperature             | -               | -40  | 125  | °C   |

<sup>1.</sup> Actual limit depends on power dissipation and  $T_J$ .

## 4 Electrical characteristics

Table 5. Electrical characteristics ( $T_J = 25~^{\circ}C$ , VH = 15 V, VDD = 5 V, unless otherwise specified)

| Symbol                | Pin             | Parameter                                                    | Test conditions                                       | Min.       | Typ.      | Max.       | Unit |

|-----------------------|-----------------|--------------------------------------------------------------|-------------------------------------------------------|------------|-----------|------------|------|

| Dynamic (             | L<br>Characteri | stics                                                        |                                                       |            |           |            |      |

| t <sub>Don</sub>      | IN+, IN-        | Input to output propagation delay ON                         | -                                                     | -          | 80        | 100        | ns   |

| t <sub>Doff</sub>     | IN+, IN-        | Input to output propagation delay OFF                        | -                                                     | -          | 80        | 100        | ns   |

| t <sub>r</sub>        | -               | Rise time                                                    | C <sub>L</sub> = 4.7 nF, 10% ÷ 90%                    | -          | 30        | -          | ns   |

| t <sub>f</sub>        | -               | Fall time                                                    | C <sub>L</sub> = 4.7 nF, 90% ÷ 10%                    | -          | 30        | -          | ns   |

| PWD                   | -               | Pulse width distortion  t <sub>Don</sub> - t <sub>Doff</sub> | -                                                     | -          | -         | 20         | ns   |

| t <sub>deglitch</sub> | IN+, IN-        | Inputs deglitch filter                                       | -                                                     | -          | 20        | 40         | ns   |

| CMTI <sup>(1)</sup>   | -               | Common-mode transient immunity,  dV <sub>ISO</sub> /dt       | V <sub>CM</sub> = 1500 V, see<br>Figure 14 on page 16 | 100        | -         | -          | V/ns |

| Supply vo             | ltage           |                                                              |                                                       |            |           | •          |      |

| VH <sub>on</sub>      | -               | VH UVLO turn-on threshold                                    | -                                                     | 8          | 9.1       | 10.5       | V    |

| VH <sub>off</sub>     | -               | VH UVLO turn-off threshold                                   | -                                                     | 7          | 8.4       | 9.5        | V    |

| VH <sub>hyst</sub>    | -               | VH UVLO hysteresis                                           | -                                                     | 0.5        | 0.9       | 1.4        | V    |

| I <sub>QHU</sub>      | -               | VH undervoltage quiescent supply current                     | VH = 4 V                                              | -          | 150       | 250        | μA   |

| I <sub>QH</sub>       | -               | VH quiescent supply current                                  | -                                                     | -          | 1.3       | 2.5        | mA   |

| I <sub>QHSBY</sub>    | -               | Standby VH quiescent supply current                          | Standby mode                                          | -          | 400       | 600        | μΑ   |

| SafeClp               | -               | GOFF active clamp                                            | I <sub>GOFF</sub> = 0.2 A;<br>VH floating             | -          | 2         | 2.5        | V    |

| I <sub>QDD</sub>      | -               | VDD quiescent supply current                                 | -                                                     | -          | 0.5       | 0.8        | mA   |

| I <sub>QDDSBY</sub>   | -               | Standby VDD quiescent supply current                         | Standby mode                                          | -          | 40        | 80         | μA   |

| Logic inputs          |                 |                                                              |                                                       |            |           |            |      |

| V <sub>il</sub>       | IN+, IN-        | Low level logic threshold voltage                            | -                                                     | 0.29 · VDD | 1/3 · VDD | 0.37 · VDD | V    |

| V <sub>ih</sub>       | IN+, IN-        | High level logic threshold voltage                           | -                                                     | 0.62 · VDD | 2/3 · VDD | 0.72 · VDD | V    |

Electrical characteristics STGAP2S

Table 5. Electrical characteristics ( $T_J$  = 25 °C, VH = 15 V, VDD = 5 V, unless otherwise specified) (continued)

| Symbol                | Pin         | Parameter                        | Test conditions                          | Min.     | Тур.     | Max. | Unit |

|-----------------------|-------------|----------------------------------|------------------------------------------|----------|----------|------|------|

| I <sub>INh</sub>      | IN+, IN-    | INx logic "1" input bias current | INx = 5 V                                | 33       | 50       | 77   | μA   |

| I <sub>INI</sub>      | IN+, IN-    | INx logic "0" input bias current | INx = GND                                | -        | -        | 1    | μA   |

| R <sub>pd</sub>       | IN+, IN-    | Inputs pull-down resistors       | INx = 5 V                                | 65       | 100      | 150  | kΩ   |

| Driver buf            | fer sectio  | n                                |                                          |          |          |      |      |

| ,                     |             | Source short-circuit             | T <sub>J</sub> = 25 °C                   | -        | 4        | -    | _    |

| I <sub>GON</sub>      | -           | current                          | $T_J = -40 \div +125  {}^{\circ}C^{(1)}$ | 3        | -        | 5    | A    |

| $V_{GONH}$            | -           | Source output high level voltage | I <sub>GON</sub> = 100 mA                | VH -0.14 | VH -0.11 | -    | V    |

| R <sub>GON</sub>      | -           | Source R <sub>DS_ON</sub>        | I <sub>GON</sub> = 100 mA                | -        | 1.11     | 1.4  | Ω    |

|                       |             | Sink short-circuit               | T <sub>J</sub> = 25 °C                   | -        | 4        | -    | ^    |

| I <sub>GOFF</sub>     | -           | current                          | $T_J = -40 \div +125  {}^{\circ}C^{(1)}$ | 3        | -        | 5.5  | A    |

| V <sub>GOFFL</sub>    | -           | Sink output low level voltage    | I <sub>GOFF</sub> = 100 mA               | -        | 84       | 95   | mV   |

| R <sub>GOFF</sub>     | -           | Sink R <sub>DS_ON</sub>          | I <sub>GOFF</sub> = 100 mA               | -        | 0.84     | 0.95 | Ω    |

| Miller Cla            | mp function | on (STGAP2SC only)               |                                          |          |          |      | l.   |

| V <sub>CLAMPth</sub>  | -           | CLAMP voltage threshold          | V <sub>CLAMP</sub> vs. GNDISO            | 1.3      | 2        | 2.6  | V    |

|                       |             |                                  | V <sub>CLAMP</sub> = 15 V                |          | -        |      |      |

| I <sub>CLAMP</sub>    | -           | CLAMP short-circuit current      | T <sub>J</sub> = 25 °C                   | -        | 4        | -    | Α    |

|                       |             |                                  | $T_J = -40 \div +125  {}^{\circ}C^{(1)}$ | 2        | -        | 5    |      |

| V <sub>CLAMP_L</sub>  | -           | CLAMP low level output voltage   | I <sub>CLAMP</sub> = 100 mA              | -        | 89       | 100  | mV   |

| R <sub>CLAMP</sub>    | -           | CLAMP R <sub>DS_ON</sub>         | I <sub>CLAMP</sub> = 100 mA              | -        | 0.89     | 1.00 | Ω    |

| Overtemp              | erature p   | rotection                        |                                          |          |          |      | l.   |

| T <sub>SD</sub>       | -           | Shutdown temperature             | -                                        | 170      | -        | -    | °C   |

| T <sub>hys</sub>      | -           | Temperature hysteresis           | -                                        | -        | 20       | -    | °C   |

| Standby               | ı           | 1                                | 1                                        | -1       |          |      | 1    |

| t <sub>STBY</sub>     | -           | Standby time                     | See Section 5.3                          | 200      | 280      | 350  | μs   |

| t <sub>WUP</sub>      | -           | Wake-up time                     | See Section 5.3                          | 10       | 20       | 35   | μs   |

| t <sub>awake</sub>    | -           | Wake-up delay                    | See Section 5.3                          | 90       | 140      | 200  | μs   |

| t <sub>stbyfilt</sub> | -           | Standby filter                   | See Section 5.3                          | 200      | 280      | 600  | ns   |

| •                     |             | 1                                | 1                                        |          |          |      |      |

<sup>1.</sup> Characterization data, not tested in production.

### 5 Functional description

#### 5.1 Gate driving power supply and UVLO

The STGAP2S is a flexible and compact gate driver with 4 A output current and rail-to-rail outputs. The device allows implementation of either unipolar or bipolar gate driving.

Figure 5. Power supply configuration for unipolar and bipolar gate driving

Undervoltage protection is available on VH supply pin. A fixed hysteresis sets the turn-off threshold, thus avoiding intermittent operation.

When VH voltage goes below the VH<sub>off</sub> threshold, the output buffer goes in "safe state". When VH voltage reaches the VH<sub>on</sub> threshold, the device returns to normal operation and sets the output according to actual input pins status.

The VDD and VH supply pins must be properly filtered with local bypass capacitors. The use of capacitors with different values in parallel provides both local storage for impulsive current supply and high-frequency filtering. The best filtering is obtained by using low-ESR SMT ceramic capacitors, which are therefore recommended. A 100 nF ceramic capacitor must be placed as close as possible to each supply pin, and a second bypass capacitor with value in the range between 1  $\mu$ F and 10  $\mu$ F should be placed close to it.

### 5.2 Power up, power down and 'safe state'

The following conditions define the "safe state":

- GOFF = ON state

- GON = high impedance

- CLAMP = ON state (for STGAP2SC)

Such conditions are maintained at power up of the isolated side (VH < VH $_{on}$ ) and during whole device power down phase (VH < VH $_{off}$ ), regardless of the value of the input pins.

The device integrates a structure which clamps the driver output to a voltage not higher than SafeClp when VH voltage is not high enough to actively turn the internal GOFF MOSFET on. If VH positive supply pin is floating or not supplied the GOFF pin is therefore clamped to a voltage smaller than SafeClp.

If the supply voltage VDD of the control section of the device is not supplied, the output is put in *safe state*, and remains in such condition until the VDD voltage returns within operative conditions.

After power-up of both isolated and low voltage side the device output state depends on the input pins' status.

**OFF**

ON

ON

#### 5.3 Control inputs

The device is controlled through the IN+ and IN- logic inputs, in accordance to the truth table described in *Table 6*.

| Input | pins | Outpu | t pins |

|-------|------|-------|--------|

| IN+   | IN-  | GON   | GOFF   |

| L     | L    | OFF   | ON     |

ON

**OFF**

**OFF**

L

Н

Η

Table 6. Inputs truth table (applicable when device is not in UVLO or "safe state")

A deglitch filter allow the input pins to ignore signals with duration shorter than  $t_{\text{deglitch}}$ , so preventing noise spikes possibly present in the application from generating unwanted commutations.

#### 5.4 Miller clamp function

L

Н

The Miller clamp function allows the control of the Miller current during the power stage switching in half-bridge configurations. When the external power transistor is in the OFF state, the driver operates to avoid the induced turn-on phenomenon that may occur when the other switch in the same leg is being turned on, due to the  $C_{GD}$  capacitance.

During the turn-off period the gate of the external switch is monitored through the CLAMP pin. The CLAMP switch is activated when gate voltage goes below the voltage threshold.  $V_{CLAMPth}$ , thus creating a low impedance path between the switch gate and the GNDISO pin.

### 5.5 Watchdog

The isolated HV side has a watchdog function in order to identify when it is not able to communicate with LV side, for example because the VDD of the LV side is not supplied. In this case the output of the driver is forced in "safe state" until communication link is properly established again.

#### 5.6 Thermal shutdown protection

The device provides a thermal shutdown protection. When junction temperature reaches the  $T_{SD}$  temperature threshold, the device is forced in "safe state". The device operation is restored as soon as the junction temperature is lower than  $T_{SD}$  -  $T_{hys}$ .

10/22 DocID031733 Rev 1

#### 5.7 Standby function

In order to reduce the power consumption of both control interface and gate driving sides the device can be put in standby mode. In standby mode the quiescent current from VDD and VH supply pins is reduced to  $I_{QDDSBY}$  and  $I_{QHSBY}$  respectively, and the output remains in 'safe state' (the output is actively forced low).

The way to enter standby is to keep both IN+ and IN- high ("standby" value) for a time longer than t<sub>STBY</sub>. During standby the inputs can change from the "stand-by" value.

To exit stand-by, IN+ and IN- must be put in any combination different from the "standby" value for a time longer than  $t_{\text{stbyfilt}}$ , and then in the "standby" value for a time t such that  $t_{\text{WLP}} < t < t_{\text{STBY}}$ .

When the input configuration is changed from the "standby" value the output is enabled and set according to inputs state after a time  $t_{awake}$ .

Figure 6. Standby state sequences Sequence to enter stand-by mode "stand-by": IN+ = IN- = HIGH  $< t_{STBY}$  $t = t_{STBY}$ XXXX is any different combination IN+ & IN-ACTIVE Device status STAND-BY ACTIVE SAFE-STATE Output Sequence to exit stand-by mode  $t > t_{STBY}$ IN+ & INstand-by STAND-BY **ACTIVE ACTIVE** Device status ACTIVE ACTIVE SAFE-STATE Output

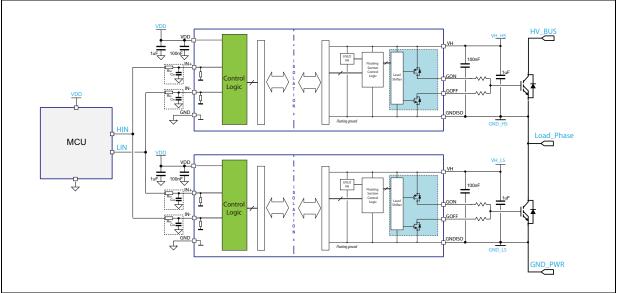

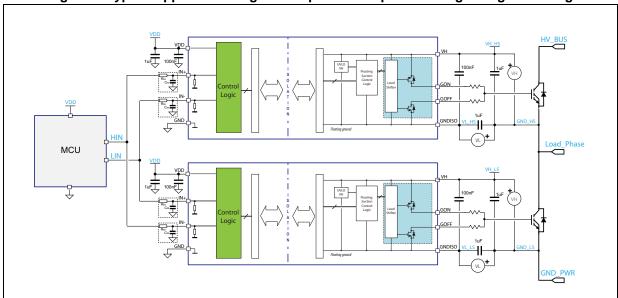

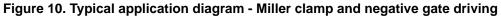

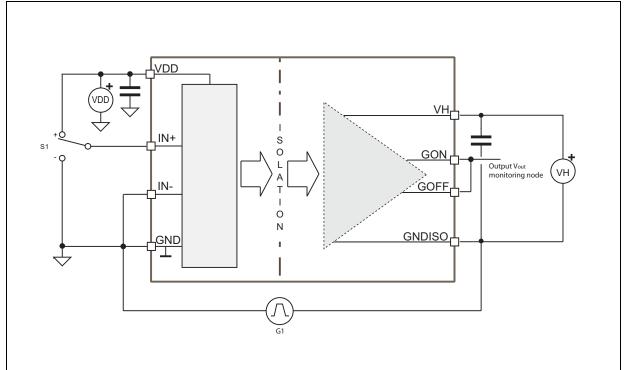

#### Typical application diagram 6

Figure 7. Typical application diagram - separated outputs

Figure 8. Typical application diagram - separated outputs and negative gate driving

577 12/22 DocID031733 Rev 1

NCU III SOUTH AND SOUTH AN

Figure 9. Typical application diagram - Miller clamp

Layout STGAP2S

### 7 Layout

#### 7.1 Layout guidelines and considerations

In order to optimize the PCB layout, following considerations should be taken into account:

• SMT ceramic capacitors (or different types of low-ESR and low-ESL capacitors) must be placed close to each supply rail pins. A 100 nF capacitor must be placed between VDD and GND and between VH and GNDISO, as close as possible to device pins, in order to filter high-frequency noise and spikes. In order to provide local storage for pulsed current a second capacitor with value in the range between 1  $\mu$ F and 10  $\mu$ F should also be placed close to the supply pins.

- As a good practice it is suggested to add filtering capacitors close to logic inputs of the device (IN+, IN-), in particular for fast switching or noisy applications.

- The power transistors must be placed as close as possible to the gate driver, so to minimize the gate loop area and inductance that might bring to noise or ringing.

- To avoid degradation of the isolation between the primary and secondary side of the driver, there should not be any trace or conductive area below the driver.

- If the system has multiple layers, it is recommended to connect the VH and GNDISO pins

to internal ground or power planes through multiple vias of adequate size. These vias

should be located close to the IC pins to maximize thermal conductivity.

577

STGAP2S Layout

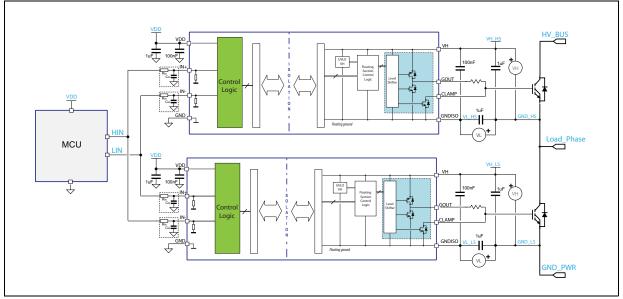

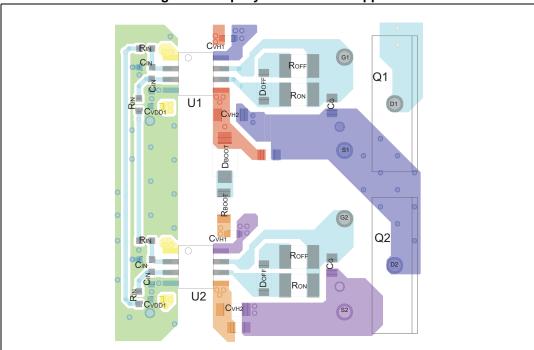

### 7.2 Layout example

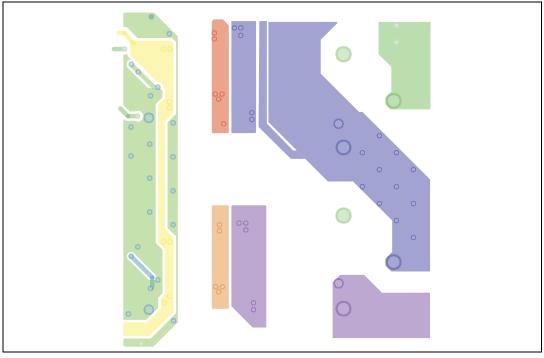

An example of STGAP2SC Half-Bridge PCB layout with main signals highlighted by different colors is shown in *Figure 11* and *Figure 12*. It is recommended to follow this example for proper positioning and connection of filtering capacitors.

Figure 11. Top layer traces and copper

# 8 Testing and characterization information

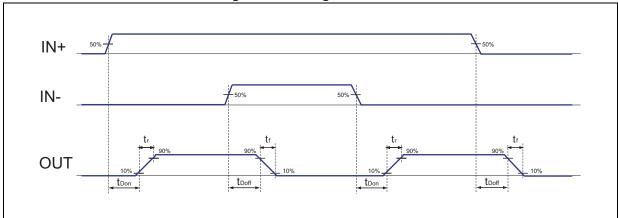

Figure 13. Timings definition

Figure 14. CMTI test circuit

5/

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

Package information STGAP2S

## 9.1 SO-8 package information

SEATING PLANE

GAGE PLANE

C

L1

L1

Figure 15. SO-8 package outline

Table 7. SO-8 package mechanical data

| Symbol | Dimensions (mm) |      |      | Notes   |

|--------|-----------------|------|------|---------|

|        | Min.            | Тур. | Max. | Notes   |

| А      | -               | -    | 1.75 | -       |

| A1     | 0.10            | -    | 0.25 | -       |

| A2     | 1.25            | -    | -    | -       |

| b      | 0.28            | -    | 0.48 | -       |

| С      | 0.17            | -    | 0.23 | -       |

| D      | 4.80            | 4.90 | 5.00 | -       |

| E      | 5.80            | 6.00 | 6.20 | -       |

| E1     | 3.80            | 3.90 | 4.00 | -       |

| е      | -               | 1.27 | -    | -       |

| h      | 0.25            | -    | 0.50 | -       |

| L      | 0.40            | -    | 1.27 | -       |

| L1     | -               | 1.04 | -    | -       |

| k      | 0               | -    | 8    | Degrees |

| ccc    | -               | -    | 0.10 | -       |

577

# 10 Suggested land pattern

0.6 (x8) 0.7 2.9

Figure 16. SO-8 suggested land pattern

Ordering information STGAP2S

# 11 Ordering information

Table 8. Device summary

| Order code  | Output configuration | Package marking | Package | Packaging     |

|-------------|----------------------|-----------------|---------|---------------|

| STGAP2SM    | GON-GOFF             | GAP2S2          | SO-8    | Tube          |

| STGAP2SMTR  | GON-GOFF             | GAP2S2          | SO-8    | Tape and reel |

| STGAP2SCM   | GOUT-CLAMP           | GAP2SC2         | SO-8    | Tube          |

| STGAP2SCMTR | GOUT-CLAMP           | GAP2SC2         | SO-8    | Tape and reel |

STGAP2S Revision history

# 12 Revision history

Table 9. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 06-Jun-2018 | 1        | Initial release. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

4

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## STMicroelectronics:

STGAP2SM STGAP2SMTR STGAP2SCM STGAP2SCMTR