# **CMOS Programmable** Divide-by-"N" Counter

Standard "A"-Series Types (3-to-15-Volt Rating)

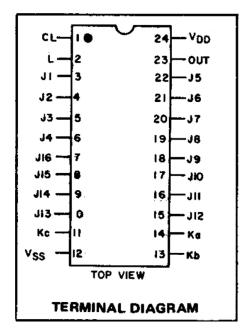

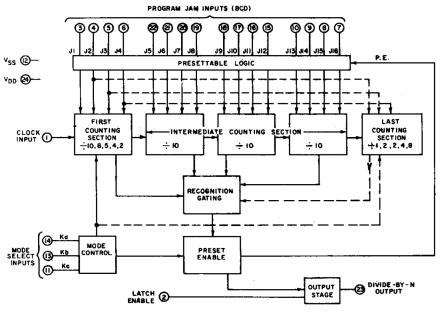

XD4059 standard"A"Series types are divide-by-N down-counters that can be programmed to divide an input frequency by any number 'N" from 3 to 15,999. The output signal is a .pulse one clock-cycle wide occurring at a rate equal to the input frequency divided by N.This single output has TTL drive capability. The down-counter is preset by means of 16 jam inputs. The three Mode-Select Inputs Ka, Kb, and Kc determine the modulus ("divide-by" Kc determine the modulus ("divide-by" number) of the first and last counting sections in accordance with the truth table shown in Table I. Every time the first (fastest) counting section goes through one cycle, it reduces by 1 the number that has been preset (jammed) into the three decades of the intermediate counting section and into of the intermediate 'counting section and into the last counting section, which consists of flip-flops that are not needed for operating flip-flops that are not needed for operating the first counting section. For example, in the÷2 mode, only one flip-flop is needed in the first counting section. Therefore the last counting section has three flip-flops that can be preset to a maximum count of seven with a place value of thousands. If ÷10 is desired for the first section, Ka Is set to 1,Kb to 1, and Kc to 0. Jam Inputs J1, J2, J3, and J4 are used to preset the first counting section and there is no' last first counting section and there is no' last counting section. The intermediate counting section consists of three cascaded BCD decade (÷10) counters presettable by means of Jam Inputs J5 through J16.

The Mode-Select Inputs permit frequency-synthesizer channel separations of 10, 12.5, 20, 25, or 50 parts. These inputs set the maximum value of N at 9999 (when the

maximum value of N at 9999 (when the first counting section divides by 5 or 10) or 15,999 (when the first counting section divides by8, 4, or 2). The three decades of the intermediate counting section can be preset to a binary 15 instead of a binary 9, while their place values are still 1, 10, and 100, multiplied by the number of the÷N mode. For example, in the ÷ 8 mode, the number from which counts the ÷ 8 mode, the number from which counting-down begins can be preset to:

3rd decade: 1500 2nd decade: 150 1st decade: Last counting section 1000

The total of these numbers (2665) times 8 equals 21,320. The first counting section can be preset to 7. Therefore, 21 ,327 is the maximum possible count in the÷8 mode. The highest count of the various modes is shown in the column entitled Extended

Counter. Range of Table 1. Control inputs Kb and Kc can be used to initiate and lock the counter in the "master preset". state. In this condition the flip-flops in the counter are preset in accordance with the jam inputs and the counter remains in that state as long as Kb and Kc both remain low. The counter begins to count down from the preset state when a counting mode other than the master preset mode is selected.

The counter should always be put in the master preset mode before the +5 mode is selected.

Whenever the master preset mode is used, control signals Kb=0 and Kc=0 must be applied for at least 3 full clock pulses.

After the Master Preset. Mode inputs have been changed to one of the÷modes, the next positive-going clock transition changes an internal flip-flop so that the countdown can begin at the second positive-going clock transition. Thus, after an MP (Master Preset) mode, there is always one extra count before the output goes high. Fig.1 ilustrates a total count of 3 (÷ 8 mode). If the Master Preset mode is started two clock cycles or less before an output pulse, the output pulse will appear at the time due. If the Master Preset Mode is not used the counter jumps back to the "JAM"count when the output pulse appears.

Fig. 1 - Total count of 3.

A "1" on the Latch Enable input will cause the counter output to remain high once an output pulse occurs, and to remain in the high state until. the latch input returns to "0". If the Latch Enable is "0", the output pulse will remain high for only .1 cycle of the clock -input signal.

As ilustrated in the sample applications, this device is particularly advantageous in com. munication digital frequency synthesis (VHF, UHF, FM, AM, etc.) where programmable divide-by."N" counters are an integral part of the cynthesizer phase legical loop subof the synthesizer phase-locked-loop sub-system. The XD4059 can also be used to perform the synthesizer "F ixed Divide-by-R" counting function. It is also useful in general-purpose counters for instrumentation func-tions such as totalizers, production counters, and "time out" timers.

### Operational and Performance Features:

- SynchronousProgrammable÷N Counter: N= 3to 9999 or 15,999

- Presettable down.counter

- Fully static operation

- Mode-select control of initial decade counting function (÷10,8,5,4,2)

- T L drive capability

- Master preset initialization Latchable + N output

- Quiescent current specified to 15 volts

Max. input leakage current of 1 µA at 15

volts,full package-temperature range

- volt noise margin, full package-temperature range

5-V and 10-V parametric ratings

### **Applications**

- Communications digital frequency synthesizers: VHF, UHF, FM, AM,etc. Fixed or programmable frequency

- division

- Time out" timer for consumer-application industrial controls

Companion Application Note,ICAN-6374,

"Applica ntlon of the CMOS XD4059

Programmable Divide-by-N Counter in

FM and Citizens Band Transceiver Digital Tuners"

# MAXIMUM RATINGS, Absolute-Maximum Values:DC SUPPLY-VOLTAGE RANGE, (VDD)Voltages referenced to $V_{SS}$ Terminal)-0.5V to +15VINPUT VOLTAGE RANGE, ALL INPUTS-0.5V to $V_{DD}$ +0.5VPOWER DISSIPATION PER PACKAGE (PD):For $T_A = -55^{\circ}$ C to +100°C500mWFOR $T_A = +100^{\circ}$ C to +125°CDerate Linearly to 100mWDEVICE DISSIPATION PER OUTPUT TRANSISTORFOR $T_A = +100^{\circ}$ C to +125°CFOR $T_A = +100^{\circ}$ C to +125°CTOOMWOPERATURE RANGE ( $T_A$ )-55°C to +125°CSTORAGE TEMPERATURE RANGE ( $T_{Stg}$ )-65°C to +150°CLEAD TEMPERATURE (DURING SOLDERING):At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79mm) from case for 10s max

### STATIC ELECTRICAL CHARACTERISTICS

|                                             | С        | onditio  |          |          |          | L        | imits. |             | •                 |           |            |  |

|---------------------------------------------|----------|----------|----------|----------|----------|----------|--------|-------------|-------------------|-----------|------------|--|

| Characteristic                              | Vo       | VIN      | VDD      | ļ        |          |          |        |             | Units             |           |            |  |

|                                             | (V)      | (V)      | (V)      | -55°     | -40°     | +850     | +1250  | +250        |                   |           |            |  |

|                                             | -        |          | <u> </u> | -        | <u> </u> |          |        | Min.        |                   | Max.      | ļ <u>.</u> |  |

| Quiescent Device                            |          |          | 5        | 10       | 10       | 700      | 300    |             | 0.02              | 10        |            |  |

| Current,                                    |          |          | 10       | 20       | 20       | 200      | 400    |             | 0.02              | 20<br>500 | μA         |  |

| IL Max.                                     |          |          | 19       |          |          |          |        |             | <u> </u>          | 300.      | L          |  |

| Output Voltage:                             |          |          | _        |          | _        |          |        |             | 1                 |           |            |  |

| Low Level                                   | <u> </u> | 0,5      | 5<br>10  | ├        |          | .05      |        | _           | 0                 | 0.05      | ļ          |  |

| VOL Max.                                    |          | 0,10     |          |          |          |          | -      | <u> </u>    | 0.05              | V         |            |  |

| High Level,                                 | <u> </u> | 0,5      | 5        | ļ        |          | .95      |        | 4.95        | 5<br>10           | -         | ļ          |  |

| VOH Min.                                    |          | 0,10     | 10       |          | 9        | .95      |        | 9.95        | 10                | -         |            |  |

| Noise Immunity:                             |          |          |          |          |          |          |        |             |                   |           |            |  |

| Inputs Low,                                 | -        |          | 5        | <u> </u> |          | 1.5      | 1,5    | 2.25        |                   | v         |            |  |

| V <sub>NL</sub> Min.                        |          | <u> </u> | 10       |          |          | 3        | 3      | 4.5         |                   |           |            |  |

| Inputs High,                                |          |          | 5<br>10  |          |          | 3        | 3      | 2,25<br>4.5 |                   |           |            |  |

| VNH Min.                                    |          |          | 10       |          |          | <u> </u> | 3      | 4.5         | _                 |           |            |  |

| Noise Margin:                               |          |          |          |          |          |          |        |             |                   |           |            |  |

| Inputs Low,                                 | 4.5      |          | 5        | 1        |          |          |        |             |                   |           |            |  |

| VNML Min.                                   | 9        |          | 10       | 1        |          |          |        |             |                   |           |            |  |

| Inputs High,                                | 0.5      |          | 5        | 1        |          |          |        |             |                   |           |            |  |

| VNMH Min.                                   | 1:       |          | 10       | 1        |          |          |        |             |                   |           |            |  |

| Output Drive<br>Current:                    |          |          |          |          |          |          |        |             |                   |           |            |  |

| N-Channel<br>(Sink)                         | 0.4      |          | 5        | 2.5      | 2.3      | 1.6      | 1.4    | 2           | 4                 |           |            |  |

| (Sink)                                      | 0.5      |          | 10       | 5        | 4.7      | 3.3      | 2.8    | 4           | 9                 |           |            |  |

| P-Channel                                   | 2.5      |          | 5        | -2       | -1.8     | -1.3     | -1.15  | -1.6        | -3.2              | -         | mA         |  |

| (Source)                                    | 4.6      |          | 5        | -0.5     | -0.45    | -0.36    | -0.3   | -0.4        | -0.8              |           | 1          |  |

| IDP Min.                                    | 9.5      |          | 10       | -1.1     | -1       | -0.75    | -0.65  | -0.9        | -1.8              | · -       |            |  |

| Input Leakage<br>Current:*<br>IIL, IIH Max. |          |          | 15       | ±10-5    |          |          |        |             | ±10 <sup>-5</sup> | ±1        | μΑ         |  |

<sup>\*</sup> Any Input

OPERATING CONDITIONS ATTA =  $25^{\circ}$  C (Unles otherwise specitied) For maximum reliability, nominal operating conditions should.be sefected so that operation u a/ways

within the following ranges.

| Characteristic                                        | VDD     | Min.       | Max.     | Units |

|-------------------------------------------------------|---------|------------|----------|-------|

| Supply Voltage<br>Range<br>(over full temp.<br>range) | L       | 3          | 12       | ٧     |

| Clock Pulse<br>Width                                  | 5<br>10 | 200<br>100 | =        | ns.   |

| Clock Input<br>Frequency                              | 5<br>10 | = .        | 1.5<br>3 | MHz   |

| Clock Input Rise<br>and Fall Time                     | 5<br>10 | _          | 15<br>5  | μs    |

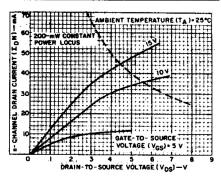

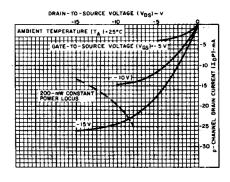

Fig.2 - Minimum output n-channel drain characteristics.

Fig.3 — Typical output n-channel drain characteristics.

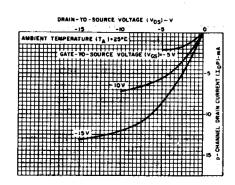

Fig.4 — Minimum output p-channel drain characteristics.

# DYNAMIC ELECTRICAL CHARACTERISTICS AT TA = 25°C, CL = 50 pF, Input $t_r, t_f$ = 20 ns, RL = 200 k $\Omega$

| CHARACTERI                           | STIC              | CONDI-<br>TIONS<br>VDD | ALI  | UNITS |          |    |  |  |

|--------------------------------------|-------------------|------------------------|------|-------|----------|----|--|--|

|                                      |                   | (V)                    | Min. | Тур.  | Max.     |    |  |  |

| Propagation Delay Time;              | tour tour         | .5                     |      | 180   | 360      | T  |  |  |

| Propagation Delay Time,              | PHL, PLH          | 10                     | _    | 90    | 180      | ns |  |  |

| Transition Time:                     |                   |                        | 1    | 1     | Γ.       |    |  |  |

|                                      | +                 | 5                      | -    | 35    | 70       |    |  |  |

|                                      | tTHL              | 10                     | _    | 20    | 40       | ١  |  |  |

|                                      |                   | 5                      |      | 100   | 200      | ns |  |  |

|                                      | <sup>t</sup> TLH  | 10                     | -    | 50    | 100      |    |  |  |

| Marrian Clark Innut Co               |                   | 5                      | 1.5  | 3     | <u> </u> |    |  |  |

| Maximum Clock Input Fr               | 10                | 3                      | 6    | -     | MHz      |    |  |  |

| Average Input Capacitano (any input) | e, C <sub>l</sub> | _                      | _    | 5     | -        | pF |  |  |

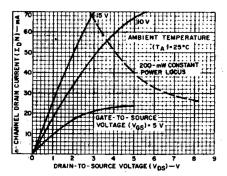

Fig.6 — Typical output p-channel drain characteristics.

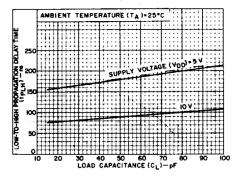

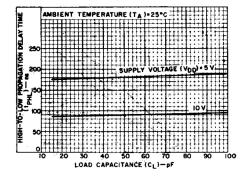

Fig.7 — Typical low-to-high propagation delay time vs. load capacitance.

Fig.8 - Typical high-to-low propagation delay time vs. load capacitance.

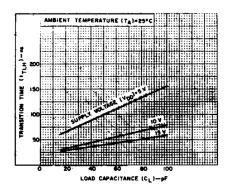

Fig.9 - Typical low-to-high transition time vs. load capacitance.

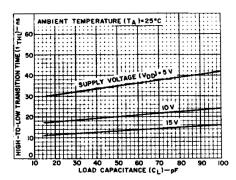

Fig. 10 — Typical high-to-low transition time vs. load capacitance.

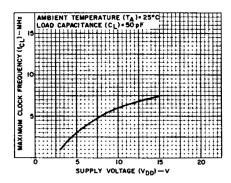

Fig.11 - Typical max. clock frequency vs. supply voltage.

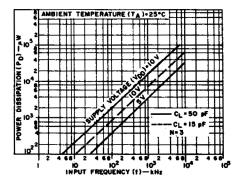

Fig. 12 — Typical power dissipation vs. input frequency.

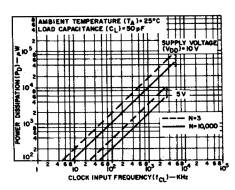

Fig.13 — Typical power dissipation vs. clock input frequency.

### TABLE I

| s  | MODE<br>SELECT<br>INPUT |     |                             | RST COU                    |                         | SECTION RANGE      |                            |                               |        | JNTER<br>ANGE<br>EXTENDED |

|----|-------------------------|-----|-----------------------------|----------------------------|-------------------------|--------------------|----------------------------|-------------------------------|--------|---------------------------|

| Ka | Kb                      | Kc  | MODE<br>Di-<br>vides<br>by: | Can be preset to a max of: | Jam≜<br>inputs<br>used: | MODE Di- vides by: | Can be preset to a max of: | Jam <sup>▲</sup> inputs used: | Max.   | Max.                      |

| 1  | 1                       | 1   | 2                           | 1                          | J1                      | 8                  | 7                          | J2,J3,J4                      | 15,999 | 17,331                    |

| 0  | 1                       | 1   | 4                           | 3                          | J1,J2                   | 4                  | 3                          | J3,J4                         | 15,999 | 18,663                    |

| 1  | 0                       | 1   | 5#                          | 4                          | J1,J2,J3                | 2                  | 1                          | J4                            | 9,999  | 13,329                    |

| 0  | 0                       | 1   | 8                           | 7                          | J1,J2,J3                | 2                  | 1                          | J4                            | 15,999 | 21,327                    |

| 1  | 1                       | . 0 | 10                          | 9                          | J1,J2,J3,J4             | 1                  | lo                         | ľ –                           | 9,999  | 16,659                    |

| ×  | 0                       | 0   | MAS                         | TER PR                     | ESET                    | MASTER PRESET      |                            |                               | _      | _                         |

X = Don't Care

▲ J1 = Least significant bit.

J4 = Most significant bit.

#Operation in the ÷5 mode (1st counting section) requires going through the Master Preset mode prior to going into the ÷5 mode. At power turn-on, kc must be a logic "O" for a period of 3 input clock pulses after V<sub>DD</sub> reaches a minimum of 3 volts. See Fig. 21 for a suggested external preset circuit.

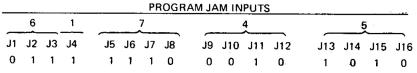

### HOW TO PRESET THE CD4059A TO DESIRED + N

The value N is determined as follows:

\* MODE= First counting section divider (10, 8, 5, 4 or 2)

To calculate preset values for any N count, divide the N count by the Mode.

The resultant is the corresponding preset values of the 5th through 2nd decade with the remainder being equal to the 1st decade value.

Preset Value =

$$\frac{N}{\text{Mode}}$$

(2)

Examples:

PROGRAM JAM INPUTS (BCD)

|   |   |   |   | • |   |   | • |   |   |   |   | J13 |   |   |   |  |

|---|---|---|---|---|---|---|---|---|---|---|---|-----|---|---|---|--|

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0   | 1 | 1 | 0 |  |

To verify the results use equation 1:

$$N = 5 (1000X 1 + 100 X 6 + 10 X 9 + 1 X 5) + 4$$

N = 8479

MODE SELECT = 8

Ka Kb Kc

To verify:

N = 8 (1000 X 1 + 100 X 5 + 10 X 4 + 1 X 7) + 6 N = 12382

MODE SELECT = 10

C) N = 8479, Mode = 10

Ka Kb Kc 1 1 0

### **PROGRAM JAM INPUTS** 8 J1 J2 J3 J4 J5 J6 J7 J8 J10 J11 J12 J13 J14 J15 J16 1 0 0 1 1 1 0 0 0 0 0 To Verify:

N = 10 (1000 X 0 + 100 X 8 + 10 X 4 + 1 X 7) + 9 N = 8479

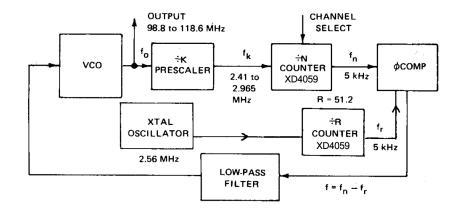

### DIGITAL PHASE-LOCKED LOOP (PLL) FOR FM BAND SYNTHESIZER

### 1) Calculating Min & Max "N" Values :

Output Freq. Range  $(\tau_0)$  = 98.8 to 118.6 MHz

Channel Spacing Freq. (f<sub>C</sub>) = 200 kHz

Division Factor (k) = 40

Reference Freq. (fr) =

$$\frac{f_C}{k} = \frac{200}{40}$$

kHz = 5 kHz

$$f_{k} = \frac{f_{0}}{40}$$

:  $f_{k}Max. = \frac{118.6 \text{ MHz}}{40} = 2.965 \text{ MHz}$ ;  $f_{k}Min = \frac{98.8 \text{ MHz}}{40} = 2.47 \text{ MHz}$

$$N = \frac{f_{0}}{f_{C}}$$

$$N_{Max} = \frac{118.6 \text{ MHz}}{200 \text{ kHz}} = 593$$

$N_{Min} = \frac{98.8 \text{ MHz}}{200 \text{ kHz}} = 494$   $R = \frac{2.56 \text{ MHz}}{5 \text{ kHz}} = 512$

### "CASCADING" VIA OTHER COUNTERS

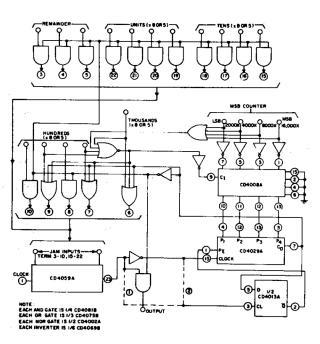

Fig. 14 shows a BCD-switch compatible arrangement suitable for ÷ 8 and ÷ 5 modes. which can be adapted, with slight changes, to the other divide-by-modes. In order to be able to preset to any number from three to about 256,000, while preserving the BCDswitch compatible character of the jam inputs, a rather complex cascading scheme is required. Such a cascading scheme is necessary because the XD4059 can never be preset to a count less than 3 and logic is needed to detect the condition that one of the numbers to be preset in the XD4059 is rather small. In order to simplify the detection logic, only that condition is detected where the jam inputs to terminals 6, 7, and 9 would be low during one count. If such a condition is detected, and if at least 1 is expected to be jammed into the MSB counter, the detection logic removes one from the number to be jammed into the MSB counter (with a place value of 2000 times the divide-by-mode) and jams the same 2000 into the XD4059 by forcing terminals 6, 7, and 9 high.

The clock of the CD4013A may be driven directly from the output of the XD4059, as shown by dashed option (1), or by the inverted output of the XD4059, option (2). If option (2) is used the XD4059 cannot count cycles shorter than 3. If option (1) is used propagation delay problems may occur at high counting speeds.

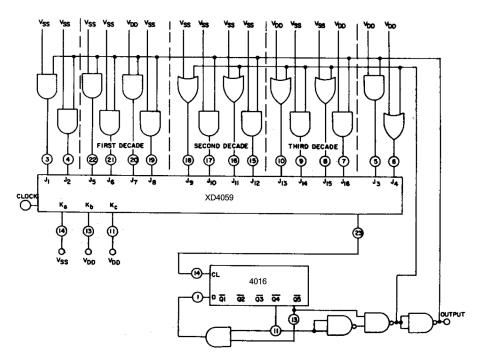

The general circuit in Fig.14 can be simplified considerably if the range of the cascaded counters does not have to start at a very low value. Fig.15 shows an arrangement in the ÷ 4 mode, where the counting range extends in a BCD-switch compatible manner from 88,003 to 103,999. The arrangement shown in Fig.15 is easy to follow; once during each cycle, the less significant digits are jammed in (14,712 in this case) and then 11,000 (4 x 2750) is jammed in eight times in succession, by forcing jam inputs high or low, as required.

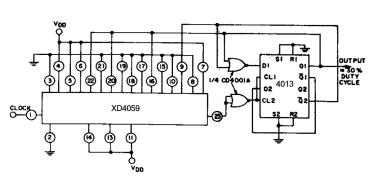

Numbers larger than the extended counter range can also be produced by cascading the XD4059 with some other counting device. Fig.16 shows such an arrangement where only one fixed divide-by number is desired which is close to three times the extended counter range as shown in the last column of Table I. The dual flip-flop wired to produce a  $\div$  3 count, can be replaced by other counters such as the XD4059, 4510 4016,4017 ot the 4022. In Fig.16

the ÷ N subsystem is preset once to a number smaller than the desired divide-by number. This smaller number represents the less significant digits of the divide-by number. The subsystem is then preset one or more times to a round number (e.g. 1000, 2000) and multiplied by the number of the divide-by mode (÷ 2 in the example of Fig.16). It is important that the second counting device has an output that is high or low, as the case may be, during only one of its counting

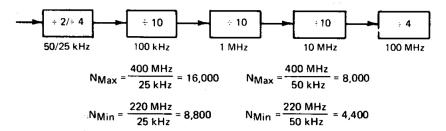

### 2) ÷ N Counter Configuration for UHF - 220 to 400 MHz Channel Spacing: 50 kHz or 25 kHz

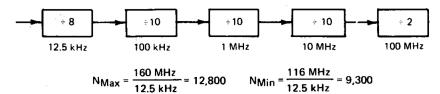

## 3) $\div$ N Counter Configuration to VHF - 116 MHz

### Channel Spacing = 12.5 kHz

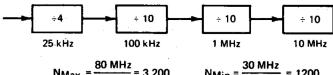

### 4) ÷ N Counter Configuration for VHF - 30 to 80 MHz Channel Spacing: 25 kHz

$$N_{Max} = \frac{80 \text{ MHz}}{25 \text{ kHz}} = 3,200$$

$N_{Min} = \frac{30 \text{ MHz}}{25 \text{ kHz}} = 1200$

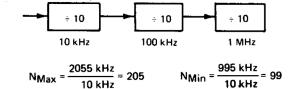

### 5) ÷ N Counter Configuration for AM - 995 to 2055 kHz Channel Spacing = 10 kHz

Fig.14 — BCD switch-compatible  $\div N$  system of the most general kind.

Fig. 15 - Dividing by any number from 88,003 to 103,999.

Fig. 16 - Division by 47,690 in ÷2 mode.

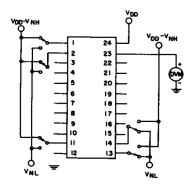

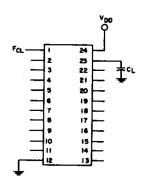

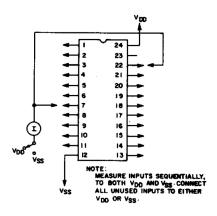

Fig.17 — Quiescent device current test circuit.

Fig. 18 — Noise immunity test circuit.

Fig.19 -- Power dissipation test circuit (ell ÷ modes).

Fig.20 - Input leakage current test circuit.

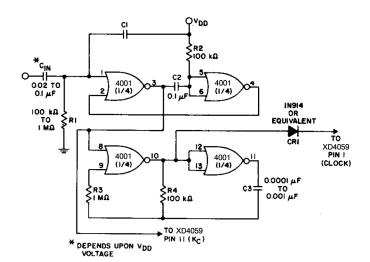

For changing from any mode other than mode 5 (with power on), apply positive pulse to  $C_{\rm in}$ . This circuit automatically selects master preset mode ( $K_b=0$ ,  $K_c=0$ ) before going into the select conditions for mode 5 ( $K_a=1$ ,  $K_b=0$ , K=1). The selection of  $C_1$  and  $C_2$  is critical.  $C_1$  is determined by the VDD voltage—the lower VDD's need larger  $C_1$ 's.  $C_2$  must be 0.1  $\mu F$  or larger.

Fig.21 - XD4059 mode 5 power on master preset circuit.

以上信息仅供参考. 如需帮助联系客服人员。谢谢 XINLUDA